Лекция

Это окончание невероятной информации про схемотехника комбинационных узлов.

...

логических элементов некоторого базиса;

Синтез КС на логических блоках является самым традиционным и изученным. В этом случае абстрактный синтез КС содержит следующие этапы:

Минимизация – это такое преобразование логических функций, которое упрощает их в смысле заданного критерия. Исторически первым критерием было стремление минимизировать число логических элементов в схеме (элементы были наиболее дорогими компонентами), что приводит к критерию сложности схемы в виде числа букв в реализуемых выражениях. Для минимизации по этому критерию разработано несколько методов, в их числе как аналитические, основанные на преобразованиях математических выражений, так и графические, основанные на применении специальных карт (карты Карно, диаграммы Вейча), удобных в использовании, если число аргументов функции не превышает 6.

Переход к заданному логическому базису от исходных выражений, которые получают в булевом базисе И, ИЛИ, НЕ, основан на применении закона двойственности (дуальности, теоремы де-Моргана).

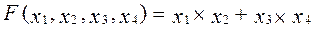

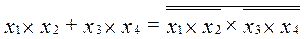

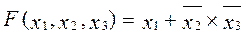

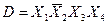

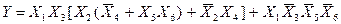

К примеру, для перехода к базису И-НЕ функции  необходимо выполнить следующее преобразования:

необходимо выполнить следующее преобразования:  . Как видим, в исходном представлении функции присутствовали как конъюнкции

. Как видим, в исходном представлении функции присутствовали как конъюнкции  и

и  , так и их дизъюнкция. В преобразованном выражении присутствуют только конъюнкции с инверсиями. Это означает, что для реализации не преобразованной функции потребуются 2 логических элемента «И» и 1 «ИЛИ», а для преобразованной – 3 ЛЭ «И-НЕ».

, так и их дизъюнкция. В преобразованном выражении присутствуют только конъюнкции с инверсиями. Это означает, что для реализации не преобразованной функции потребуются 2 логических элемента «И» и 1 «ИЛИ», а для преобразованной – 3 ЛЭ «И-НЕ».

Различные методы выполнения абстрактного синтеза КС на базе логических блоков и на основе мультиплексоров были использованы ранее в этом разделе при рассмотрении наиболее распространенных комбинационных узлов, выпускаемых в виде микросхем – шифраторов, компараторов, мультиплексоров и т.д.

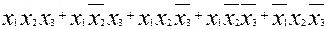

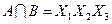

Для синтеза КС на основе логических блоков табличного типа обязательно необходимо чтобы функция была представлена в СДНФ. Дело в том, что табличный блок представляет собою память, в которой имеется столько ячеек, сколько необходимо для хранения всех значений функций, т.е. 2m, где m – число аргументов функций. При этом, набор аргументов является адресом той ячейки, в которой хранится значение функции на данной наборе (0 или 1). СДНФ как раз и содержит все адреса, по которым нужно хранить единичные значения функции. Если функция выражена в какой-либо сокращенной форме, то следует перевести ее в СДНФ. Для этого конъюнктивные члены, не содержащие переменной  , умножаются на равную единице дизъюнкцию

, умножаются на равную единице дизъюнкцию  . К примеру, функция вида

. К примеру, функция вида  после умножения

после умножения  на

на  и

и  , а

, а  на

на  примет вид:

примет вид:

или, опустив знак конъюнкции -

или, опустив знак конъюнкции -  .

.

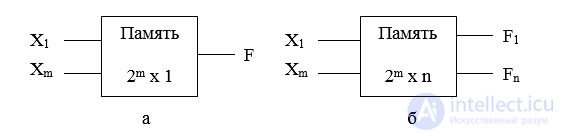

Блок памяти для воспроизведения функции m переменных имеет вид, представленный на рис. 3.28.а. Если требуется воспроизвести n функций, то в каждой ячейке нужно будет хранить бит (по одному биту для каждой функции), и блок памяти должен быть организован так, как показано на рис. 3.28.б.

Если размерность блоков табличного типа такова, что не позволяет получить искомую функцию с помощью одного блока, т.е. число входов блока памяти меньше числа аргументов функции, то появляется необходимость решения сложной задачи выражения искомой функции через подфункции с меньшим числом аргументов.

Рис. 3.28 Блоки памяти для воспроизведения одной (а) и нескольких (б) логических функций

В случае реализации проекта на логических блоках в виде последовательно включенных матриц элементов И и ИЛИ либо их эквивалентов в другом базисе, то исходную СДНФ можно минимизировать, если, конечно возникает такая необходимость. Логические блоки с матрицами И и ИЛИ воспроизводят системы переключательных функций и имеют параметры: число входов, выходов и термов. Число входов (аргументов воспроизводимых функций) и число выходов (самих функций) от формы выражения функций не зависят и предопределены заданием. Число термов (имеются в виду конъюнктивные термы) зависит от формы представления функций системы. Если число термов при данной форме представления функции превышает возможности логического блока, то возникает вопрос о минимизации функции. Целью минимизации будет сокращение числа конъюнктивных термов в данной системе функций, т.е. поиск кратчайших дизъюнктивных форм. Практически это сводится к поиску минимальных дизъюнктивных нормальных форм (МДНФ) и отбору среди них вариантов с достаточно малым числом термов. Как только находится форма с достаточно малым числом термов, поиск других форм можно прекратить, т.к. дальнейшее уменьшение числа термов системы эффекта не даст: сложность аппаратных средств воспроизведения системы не уменьшится. Разумеется, речь идет о реализации на уже выбранных средствах, а не о том, что могут быть применены иные логические блоки – того же типа, но иной размерности.

Из этапов схемного синтеза комбинационных узлов далее более детально рассмотрим этап построения принципиальных схем, т.к. этап перехода в требуемый базис в зависимости от средств реализации функций, примененных при проведении абстрактного синтеза, уже либо выполнен в процессе абстрактного синтеза, либо вообще не требуется потому, что в качестве таких средств реализации выбраны ИС более высокой степени интеграции. Что касается разработки монтажной схемы, изготовления устройства и его испытания, то это вопросы, относящиеся к компетенции конструкторов и непосредственно изготовителей, поэтому в процессе освоения данной дисциплины рассматриваться не будут.

В первую очередь в процессе схемного синтеза на этапе разработки принципиальных схем необходимо обратить внимание на соблюдение выполнения следующих основных параметров используемых в проекте ИС.

Питающие напряжения ИС, которые, в случае применения в проекте различных серий, могут быть разными для выбранных ИС. С целью достижения минимальной стоимости проекта необходимо добиваться минимального количества питающих напряжений, либо принять необходимые меры, таких, как введение в принципиальную схему специальных электронных устройств, позволяющих получать из одного питающего напряжения (к примеру, +12 В), требуемых для функционирования всех ИС (к примеру, +6 В и 3.3 В).

Уровни логических сигналов для представления лог. «0» и лог. «1», в случае применения ИС разных серий. В данном случае речь идет об электрической совместимости цифровых схем,суть которой заключается в обеспечении согласованности полярности и уровней напряжений логического “0” и логической “1”.

Нагрузочная способность (коэффициент разветвления по выходу). Коэффициент разветвления по выходу (Краз) показывает на какое количество логических входов может быть одновременно нагружен выход данного логического элемента. Обычно Краз для наиболее часто используемых серий равен 10. Иногда вместо Краз задается предельно допустимое значение выходного тока логического элемента в состоянии «0» или «1».

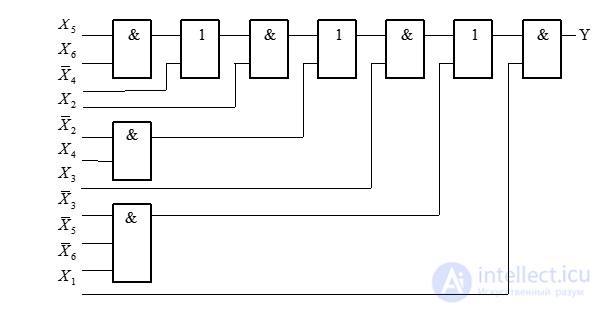

При построении КУ может оказаться, что выход k-го логического элемента нагружен n > Краз входов других ЛЭ (рис. 3.29,а). Это означает, что k-й логический элемент перегружен и необходимо принять меры, устраняющие указанное явление. Существуют два способа обеспечения заданного Краз:

· использование дополнительных развязывающих усилителей;

· дублирование перегруженного элемента.

Схема с использованием дополнительных развязывающих усилителей представлена на рис. 3.29,б. Количество p дополнительных усилителей, необходимых для обеспечения заданногоКраз, определяется по формуле:

p > (n - Краз) / (Краз - 1)

Недостаток рассматриваемого способа в том, что в цепь распространения сигнала вносится дополнительная задержка, что не всегда допустимо.

Схема с использованием дублирования перегружаемого элемента представлена на рис. 3.29,в. Количество p дополнительных элементов, выполняющих ту же функцию, что и k-й элемент, определяется по формуле: p > Краз.

При таком способе обеспечения Краз дополнительная задержка не вносится, но увеличивается нагрузка на элементы, формирующие сигналы  и

и  , что может привести к перегрузке этих элементов и введению дополнительных элементов для обеспечения заданного Краз.

, что может привести к перегрузке этих элементов и введению дополнительных элементов для обеспечения заданного Краз.

Рис. 3.29. Способы обеспечения требуемого Краз.

Рис. 3.29. Способы обеспечения требуемого Краз.

Коэффициент объединения по входу (Коб) определяет максимально возможное число входов логического элемента, иными словами, функцию скольких переменных может реализовать этот элемент. Обычно Коб принимает значение от 2 до 4, реже Коб= 8. Увеличение числа входов связано с усложнением схемы элементов и приводит к ухудшению других параметров – помехоустойчивости, быстродействия и т.д.

Представлению функции в виде ДНФ соответствует двухуровневая КС (если считать, что на ее вход могут поступать как прямые так и инверсные входные сигналы), на первом уровне которой элементы И, а их выходы объединяются на втором уровне элементом ИЛИ. Такое построение КС обеспечивает ее максимальное быстродействие, так как ранг схемы минимален. Однако, не всегда возможно на первом уровне и, особенно, на втором выбрать логические элементы с требуемым Коб, т.к. может оказаться, что ЛЭ с таким Коб не выпускаются промышленностью. В этом случае необходимо с помощью нескольких элементов с меньшим Кобполучить эквивалент с большим Коб либо, что предпочтительней, преобразовать БФ, перейдя от ДНФ к скобочной форме. Этот переход сопровождается уменьшением Коб логических элементов, требуемого для построения схемы. Осуществить такой переход можно с помощью факторного алгоритма, суть которого рассмотрим на примере.

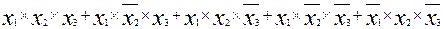

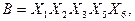

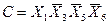

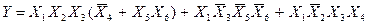

Пусть задана некоторая булева функция в виде:

Для реализации этой функции по приведенному выражению необходимо использовать 3 логических элемента 4И, один логический элемент 5И и один логический элемент 4ИЛИ.

С помощью факторного алгоритма получим скобочную форму для заданной функции. Для этого обозначим все конъюнкции буквами:

,

,

и будем рассматривать их как некоторые множества. Находим попарные пересечения множеств:

,

,  ,

,  ,

,  ,

,  ,

,  .

.

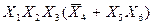

Полученные пересечения показывают общие части отдельных конъюнкций. Выбираем пересечение, которое имеет наибольшую длину (если такое отсутствует, то выбирают то, которое чаще всего встречается). В данном случае это  . Поэтому из конъюнкций А и В выносим общую часть

. Поэтому из конъюнкций А и В выносим общую часть . Тогда имеем:

. Тогда имеем:

.

.

Обозначим F =  и находим пересечения:

и находим пересечения:

,

,  ,

,

Следовательно, для исходной функции имеем:

.

.

Обозначим  ,

,

Пересечение . Следовательно, окончательно имеем:

. Следовательно, окончательно имеем:

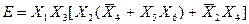

Для реализации функции по последнему выражению необходимо 5 элементов 2И, 1 элемент 3И и 3 элемента 2ИЛИ (рис. 3.30).

Рис. 3.30 Функциональная схема, полученная на основании факторного алгоритма

Как видно из полученной схемы, для ее реализации необходимы элементы с Коб = 2 или 3 (в отличие от исходной схемы с Коб = 4 или 5). Однако ранг схемы увеличился до 7, что приводит к увеличению задержки срабатывания схемы.

На такой параметр, как быстродействие проектируемой схемы оказывает существенное влияние два фактора: задержка, вносимая каждым элементом ИС, участвующим в функционировании этой схемы и количество последовательно подключенных такихэлементов в цепи формирования выходного сигнала. Если существует несколько параллельно соединенных последовательных цепей, участвующих в формировании выходного сигнала, то быстродействие схемы вычисляется по значению задержки той последовательной цепочке, которая вносит максимальную задержку. Помимо этого, на быстродействие цифровой схемы определяется еще и задержками в цепях соединений между ИС, входящими в проектируемую схему. Значение этих задержек зависит от длины проводников, их взаимного расположения и расстояния между ними. С учетом того, что эти параметры определяются на этапе разработки монтажной схемы и изготовления устройства, и, если предполагается эксплуатация разрабатываемого устройства на частотах, близких к максимально допустимым, необходимо на этих этапах разработки принимать необходимые меры по минимизации такого типа задержек.

Помехоустойчивость – это параметр, определяющий уровень значений импульсных помех, возникающих в цепях ЦУ питания в процессе его работы.

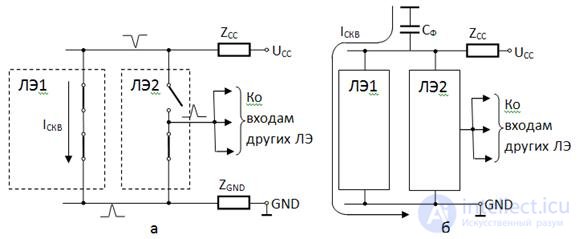

Типовой проблемой в данном случае является, в частности, наличие токовых импульсов в цепях питания ИС, которые создаются сквозными токами выходных каскадов типа и токами перезаряда емкостей.

Импульс сквозного тока переключающего ЛЭ1 (рис. 3.31,а) IСКВ протекает через транзисторы выходного каскада, условно изображенные замкнутыми ключами, от источника питания UCC на общую точку схемы GND через линии, имеющие полные сопротивленияZCC и ZGND. Главную часть сопротивлений составляют индуктивности линий, на которых выделяются напряжения UL=Ldi/dt. Протекание сквозного тока создает на линии питания отрицательный импульс, а на линии общей точки («земли») – положительный.

Эти импульсы воздействуют на подключенный вблизи элемента ЛЭ1 элемент ЛЭ2. Если, как показано на рисунке, ЛЭ2 находится в состоянии лог. «0», то его выход через насыщенный транзистор выходного каскада, отображаемый замкнутым ключом, связан с линией GND, следовательно, импульс с этой линии попадает на выход ЛЭ2. При единичном состоянии элемента ЛЭ2 на его выход пройдет отрицательный импульс помехи с линии источника питания.

Рис. 3.31. Схемы, поясняющие процесс возникновения импульсных помех при переключении ЦЭ (а), и пути протекания сквозного тока при наличии в схеме фильтрующего конденсатора (б)

Для борьбы с этими опасными помехами нужны «хорошая земля» и фильтрация напряжения питания. Качество «земли» улучшается конструктивными мерами, снижающими сопротивление ZGND: шины «земли» делают утолщенными, нередко для их реализации на печатных платах отводят целые плоскости многослойных конструкций, систему заземления соединяют с несколькими выводами на входных разъемах, чтобы сократить пути прохождения токов в этой системе и уменьшить активное сопротивление на контактах разъемов.

Для шин питания схемы наряду с конструктивными методами борьбы с помехой применяют и схемотехнические:

Для фильтрации напряжений питания между линией UCC и «землей» включают конденсаторы. Высокая эффективность этого метода борьбы с паразитными связями элементов через цепи питания связана со следующим обстоятельством. ЦУ питаются от высококачественных источников стабилизированного питания, внутреннее сопротивление которых достаточно мало. Однако цепи обратной связи этих источников инерционны и не успевают отрабатывать короткие импульсы помехи. Поэтому для коротких помех выходное сопротивление источника питания не обеспечивает того низкого уровня, которое оно имеет при статическом режиме работы ЦУ. Установка фильтрующих конденсаторов СФ создает путь (рис. 3.31,б), по которому замыкаются импульсы сквозного тока и токи перезарядки емкостей, минуя сопротивление UCC. Естественно, конденсаторы должны иметь малое сопротивление для высокочастотных сигналов, поэтому для фильтрации выбирают те типы конденсаторов, которые имеют малые паразитные индуктивности. Рекомендации по числу, типу и емкости фильтрующих конденсаторов вырабатываются практикой и приводятся в руководящих материалах по применению конкретных типов ИС.

В завершении рассмотрения проблем борьбы с помехами следует сказать, что на практике диапазон допустимых значений этих помех находится в диапазоне 0,6-0,9 В.

В завершении рассмотрения проблем борьбы с помехами следует сказать, что на практике диапазон допустимых значений этих помех находится в диапазоне 0,6-0,9 В.

Значениерассеиваемой мощности или мощности потребления ИС и другими элементами проектируемого ЦУ необходимо знать для того, чтобы сформулировать требования к источникам питания и конструкции теплоотводов. Применение теплоотводов необходимо в тех случаях, когда для поглощения рассеиваемой элементами схемы устройства мощности не достаточно ее естественного отбора. Необходимо помнить о том, что суммарная рассеиваемая мощность складывается из статической и динамической составляющих. И, если значение величины статической мощности можно получить из справочных данных на применяемые в схеме элементы, то значение динамической мощности, т.е. мощности, потребляемой элементами в процессе их переключения из одного состояния в другое, можно узнать только расчетным путем. При этом необходимо понимать, что основным параметром, определяющим уровень динамической мощности, является тактоваячастота работы ЦУ.

С учетом того, что при постановке задачи синтеза или в процессе абстрактного синтеза КУ в качестве базовых элементов могут быть выбраны цифровые элементы с открытым коллектором (стоком), открытым эмиттером (истоком) или с выходом, имеющим третье состояние (высокого импеданса), на этапе разработки принципиальных схем таких устройств необходимо учитывать особенности соединения входов и выходов этих элементов, а также их подключения к цепям питания. Помимо этого в разрабатываемом КУ необходимо предусмотреть схемное решение управления выдачей сигналов с этих элементов с целью недопущения одновременной выдачи в одну и ту же линию сигналов с выходов нескольких элементов схемы.

Для предотвращения одновременной выдачи сигналов на выходную линию с нескольких элементов, имеющих третье состояние, в таких элементах предусмотрен сигнал управления, обычно называемый ОЕ (Output Enable). При наличии разрешения (ОЕ=1) элемент работает как обычно, выполняя свою функцию, а при его отсутствии (ОЕ=0) переходит в состояние «отключено». Выходы таких элементов можно соединять параллельно, т.е. подключать к одной линии, при условии, что в любой момент времени активным может быть только один из них. В этом случае отключенные выходы не мешают активному формировать сигналы в точке соединения выходов. Такие элементы требуют обязательного соблюдения условияОЕ1+ ОЕ2+…+ ОЕn≤1 при соединении nвыходов. Нарушение этого условия может привести даже к выходу из строя самих элементов.

В случае применения элементов с открытым коллектором (стоком) для формирования высокого уровня выходного напряжения при запирании выходного транзистора такого элемента требуется подключать внешние резисторы, соединенные с источником питания. Значение сопротивления этих резисторов зависит от количества элементов, подключенных к одному и тому же выходу. Это обстоятельство позволяет повысить нагрузочную способность элемента с ОК по сравнению с обычными ЛЭ. Необходимо понимать, что большое сопротивление нагрузочных резисторов приводит к снижению быстродействия элементов с ОК. Окончательно значение сопротивления нагрузочного резистора выбирается с учетом быстродействия схемы и потребляемой ею мощности. Помимо этого, если выходы нескольких элементов с ОК подключены параллельно, можно реализовать либо дополнительную монтажную логику, либо параллельную работу элементов с ОК на одну выходную линию, аналогично тому, как это делается на элементах ТС. При этом в качестве сигнала ОЕ для элементов ТС в элементах с ОК может быть использован один из обычных входов элементов. Если речь идет об элементе И-НЕ, то, подавая лог. «0» на любой из входов, можно запретить работу этого элемента, поставив его выход в разомкнутое состояние независимо от состояния других входов.

К проблематике проектирования цифровых устройств, в том числе и КС, относится и вопрос о критериях их качества. Поскольку одну и ту же задачу можно решить многими способами, возникают альтернативные варианты проекта, которые нужно уметь сравнивать между собой. Объективная сложность сравнительной оценки вариантов обусловлена тем, что при этом имеет значение целый набор свойств для каждого варианта – частных критериев его качества. Каждый частный критерий имеет ясный, определенный смысл (аппаратная сложность, быстродействие, потребляемая мощность, помехоустойчивость и др.), но не может исчерпывающим образом охарактеризовать вариант. Чтобы учесть несколько частных критериев качества, нужно сформировать общий критерий (интегральный, многоцелевой, функцию качества, функцию ценности). Формирование такого критерия – чрезвычайно ответственная задача, не имеющая формального решения. В любую форму общего критерия входят коэффициенты, назначаемые субъективно. Таким образом, возникает ситуация, когда для оценки устройства применяется критерий, а для него самого оценки качества не существует. Поэтому на практике проектирования сложные общие критерии оценки качества не популярны. Наиболее признанным считается критерийсложность-быстродействие.

Сложность схемы оценивается количеством оборудования, составляющего схему. При разработке схем на основе конкретной элементной базы количество оборудования обычно измеряется числом корпусов (модулей) интегральных микросхем, используемых в схеме. В теоретических разработках ориентируются на произвольную элементную базу и поэтому для оценки затрат оборудования используется оценка сложности схем по Квайну.

Сложность (цена) по Квайну определяется суммарным числом входов логических элементов в составе схемы.

При такой оценке единица сложности – один вход логического элемента. Цена инверсного входа обычно принимается равной двум. Такой подход к оценке сложности оправдан по следующим причинам:

- сложность схемы легко вычисляется по булевым функциям, на основе которых строится схема: для ДНФ сложность схемы равна сумме количества букв, (букве со знаком отрицания соответствует цена 2), и количества знаков дизъюнкции, увеличенного на 1 для каждого дизъюнктивного выражения.

- все классические методы минимизации булевых функций обеспечивают минимальность схемы именно в смысле цены по Квайну.

Практика показывает, что схема с минимальной ценой по Квайну обычно реализуется наименьшим числом конструктивных элементов – корпусов интегральных микросхем.

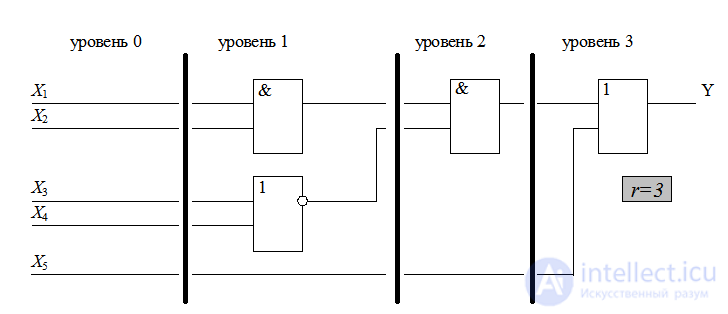

Быстродействие комбинационной схемы оценивается максимальной задержкой сигнала при прохождении его от входа схемы к выходу, т.е. определяется промежутком времени от момента поступления входных сигналов до момента установления соответствующих значений выходных. Задержка сигнала кратна числу элементов, через которые проходит сигнал от входа к выходу схемы. Поэтому быстродействие схемы характеризуется значением rt, где t- задержка сигнала на одном элементе. Значение r определяется количеством уровней комбинационной схемы, которое рассчитывается следующим образом. Входам КС приписывается уровень 0. Логические элементы, связанные только с входами схемы относятся к уровню 1. Элемент относится к уровню k, если он связан по входам с элементами уровней k-1, k-2, и т.д. Максимальный уровень элементов r определяет количество уровней КС, называемое рангом схемы. Пример определения ранга r схемы приведен на рисунке 3.32.

Рис. 3.32 Определение ранга схемы

Таким образом, после получения в результате синтеза несколько вариантов технической реализации КС и проведения оценки качества реализации каждого из вариантов, принимается окончательное решение по выбору того варианта схемы, у которой минимальный коэффициент сложности (минимальная цена) и максимальное быстродействие.

Надеюсь, эта статья про схемотехника комбинационных узлов, была вам полезна, счастья и удачи в ваших начинаниях! Надеюсь, что теперь ты понял что такое схемотехника комбинационных узлов и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Компьютерная схемотехника и архитектура компьютеров

Часть 1 Тема 3. Схемотехника комбинационных узлов

Часть 2 3.6 Синтез КС на основе мультиплексоров - Тема 3. Схемотехника

Часть 3 3.11.2 Основные факторы, которые должны быть учтены при построении принципиальных

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров