Лекция

Привет, сегодня поговорим про универсальные микропроцессоры, обещаю рассказать все что знаю. Для того чтобы лучше понимать что такое универсальные микропроцессоры, архитектура процессора кр580вм80 , настоятельно рекомендую прочитать все из категории Компьютерная схемотехника и архитектура компьютеров.

В разделе 12 уже рассматривались принципы функционирования элементарного гипотетического микропроцессора (термин "микропроцессор" и "процессор" далее используются как синонимы). Между тем для изучения принципов функционирования даже простейшей микроЭВМ необходимо выбрать конкретный тип процессора с конкретной системой команд и управляющих сигналов. Примером простейшего универсального процессора (т.е. процессора с универсальной системой команд) аккумуляторного типа является I8080 (отечественный аналог КР580ВМ80А), выпущенный Intel в 1974 году. В этом же году на процессоре I8080 был спроектирован компьютер "Альтаир 8800", который некоторые эксперты называют первым персональным компьютером в истории развития техники. Именно это поколение 8-разрядных МП (I8080, I8085, Z80 и др.) стало широко применяться в управляющих микроЭВМ, контроллерах АСУ ТП, микрокомпьютерах общего назначения и в учрежденческой деятельности, в основном для обработки текстов.

Процессор I8080 имеет 8-разрядное АЛУ и УУ, выполненные на одном кристалле, содержащем около 5000 транзисторов. БИС МП имеет 40 выводов. Управляющее устройство выполнено на ПЛМ и недоступно пользователю, т.е. процессор имеет фиксированную систему команд. Напряжение питания ±5 В и +12 В. МП имеет двухфазную синхронизацию (F1 и F2) при тактовой частоте до 2,5 МГц и следующие шины:

· ША – 16-разрядная. Используется для адресации:

- ОЗУ, ПЗУ (команды R/W) – 16 разрядов (адресное пространство составляет 64 К);

- ПУ (команды I/O) – 8 разрядов (256 адресов);

· ШД – 8-разрядная, двунаправленная. Используется:

- для приема операндов и команд от памяти и ПУ;

- выдачи данных (результатов) в память и ПУ;

· ШУ – отдельно не оформлена и имеет 10 линий, по которым передаются 4 входных и 6 выходных сигналов.

Условное обозначение МП на схемах приведено на рис. 16.1.

Рассмотрим коротко, без подробных пояснений, назначение управляющих сигналов, учитывая, что ряд входных и выходных сигналов образуют как бы пары, отвечая за те или иные действия МП.

Рис.16.1. Условное обозначение МП КР580ВМ80

Управление прерыванием

INT – входной сигнал запроса прерываний от ПУ, воспринимаемый МП после выполнения текущей команды. Сигнал не воспринимается, если МП находится в режиме захвата или запрещения прерывания.

INTE – выходной сигнал разрешения прерывания. Этот сигнал отражает состояние внутреннего триггера "разрешение прерывания", который устанавливается только программно.

Управление режимом ожидания

READY – входной сигнал готовности, который сообщает о готовности устройства вести обмен с МП. При его отсутствии МП переходит в состояние ожидания. Позволяет синхронизировать работу МП и более медленной памяти или ПУ. Сигнал READY может задаваться как с ПУ, так и со вспомогательного таймера. В простейших устройствах этот вход не используется и подключается через сопротивление к источнику +5 В.

WAIT – выходной сигнал ожидания, подтверждающий, что МП находится в режиме ожидания.

Управление обменом информации

HOLD (HLD) – входной сигнал захвата шин от ПУ. Переводит буферы ША и ШД МП в третье состояние (состояние Z) , т.е. МП отключается от шин. Это позволяет ПУ занимать магистраль для инициализации обмена

HLDA – выходной сигнал подтверждения состояния захвата МП.

Управление чтением/записью

DBIN – выходной сигнал приема. Указывает памяти и ПУ, что ШД находится в режиме приема информации в МП, т.е. в режиме чтения.

– выходной сигнал выдачи. Используется для управления выдачей информации из МП в память и ПУ (режим записи). Активным является

– выходной сигнал выдачи. Используется для управления выдачей информации из МП в память и ПУ (режим записи). Активным является

= 0.

= 0.

Управление счетчиком команд

RESET – входной сигнал сброса. Устанавливает в 0 счетчик адреса команд.

Синхронизация

SYNC – выходной сигнал синхронизации. Указывает на начало каждого нового машинного цикла.

F1, F2 – синхропоследовательности, определяющие такт работы МП. Задаются кварцованным генератором.

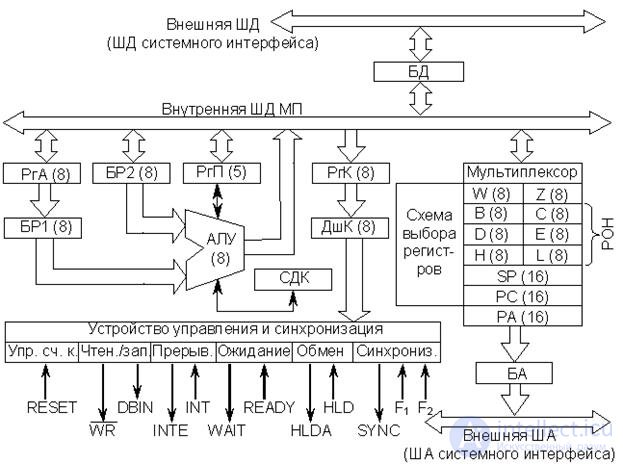

Упрощенная функциональная схема МП изображена на рис. 16.2. На схеме изображены только функциональные связи между основными узлами МП. Цепи передачи управляющих сигналов, порождающих соответствующие микрооперации в узлах МП, на рисунке отсутствуют. В скобках указана разрядность устройств МП.

Для хранения участвующих в операции данных предусмотрены семь 8-разрядных регистров. РгА, называемый аккумулятором, предназначен для обмена информацией с памятью и ПУ, т.е. его содержимое может быть выдано на ШД либо число с ШД записано в него. При выполнении арифметических, логических операций и операций сдвига он служит источником операнда. В него же всегда помещается результат выполнения операций.

Шесть других регистров называются B, C, D, E, H, L и образуют блок регистров общего назначения – РОН. Эти регистры программно доступны, и обращение к ним осуществляется посредством команд передачи данных. Причем обмен данными внутри МП (т.е. между РОН, АЛУ и аккумулятором) осуществляется по внутренней 8-разрядной шине через двунаправленный мультиплексор. РОН могут хранить как данные, так и адреса. Эти регистры можно использовать двояко – как одиночные восьмиразрядные регистры и как регистровые пары BC, DE, HL для хранения 16-разрядных двоичных чисел.

Рис.16.2. Об этом говорит сайт https://intellect.icu . Функциональная схема МП

Регистры БР1, БР2, W, Z используются как буферные и программно недоступны (т.е. их содержимое посредством команд пользователь изменять не может).

Указатель стека SP служит для адресации стековой памяти и может хранить 16-разрядные адреса.

Счетчик адреса команд PC предназначен для хранения 16-разрядного адреса команды, а точнее, адреса текущего байта команды, поскольку команды могут занимать 1, 2, 3 байта. После выборки из памяти текущего байта содержимое счетчика увеличивается на 1, т.е. формируется адрес следующего байта. При обращении к памяти (если используется косвенная адресация) в качестве адреса может использоваться содержимое любой регистровой пары РОН.

При выдаче адреса содержимое соответствующих регистров передается в 16-разрядный регистр адреса (РА), из которого далее через БА адрес поступает на ША системного интерфейса.

МП имеет 8-разрядное АЛУ, которое позволяет выполнять 4 арифметические операции (сложение с передачей переноса в младший разряд и без него, вычитание с передачей займа в младший разряд и без него), четыре вида логических операций (конъюнкция дизъюнкция, неравнозначность, сравнение), а также 4 вида циклических сдвигов.

При выполнении арифметических операций одним из операндов всегда является содержимое аккумулятора. Результат всегда помещается в аккумулятор. Циклический сдвиг выполняется только над содержимым аккумулятора.

Предусмотрена возможность выполнения арифметических операций над десятичными числами. При этом в байт укладываются две десятичные цифры в коде 8421. При рассмотрении операций десятичной арифметики отмечалось, что может потребоваться коррекция результата, т.е. прибавление к нему числа 0110(2). Такая коррекция в каждой тетраде результата осуществляется схемой десятичной коррекции (СДК).

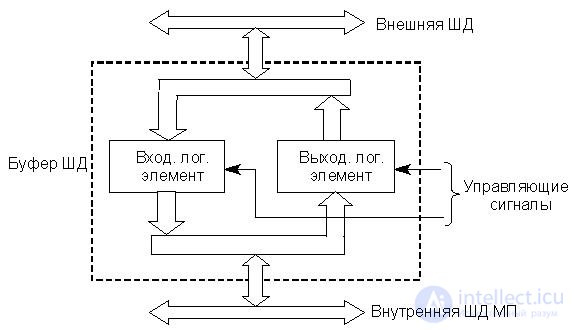

Ранее отмечалось, что РгП называют еще регистром флажков и обозначают часто буквами Ф или F. Это 8-разрядный регистр, в котором используются только 5 разрядов. Он предназначен для хранения ряда признаков, выявляемых в числе, которое является результатом операции в АЛУ или РОН. Триггеры регистра имеют следующее назначение:

Tc (триггер переноса) – устанавливается в 1 при наличии переноса из старшего разряда при выполнении арифметических операций (c=1 – перенос есть; c=0 – переноса нет). Кроме того, запоминает содержимое выдвигаемого из аккумулятора разряда при выполнении операции сдвига.

Tz (триггер нуля) – устанавливается в состояние логической 1, если результат операции в АЛУ или операции приращения содержимого РОН равен 0 (z=1 – результат равен 0, z=0 – результат не 0).

Ts (триггер знака) – устанавливается в состояние, соответствующее значению старшего разряда результата операции в АЛУ или операции приращения содержимого РОН (s=0 – результат положительный, s=1 – результат отрицательный).

Tp (триггер четности) – устанавливается в состояние логической 1, если число единиц в разрядах результата четно (p=1 – вес результата четный, p=0 – нечетный).

Tv (триггер дополнительного переноса) хранит перенос из 3-го разряда, возникающий при выполнении операции в АЛУ.

Состоит из регистра команд, куда принимается первый байт команды, дешифратора команд и непосредственно управляющего устройства, формирующего управляющие сигналы, под действием которых выполняются последовательности микроопераций в отдельных узлах МП. Как уже отмечалось, управляющее устройство выполнено на ПЛМ, т.е. микропрограммы хранятся за счет системы жестких связей и не могут быть изменены пользователем. Четыре входных и шесть выходных сигналов управляющего устройства при наличии системного контроллера позволяют процессору управлять вычислительными системами достаточно сложной структуры.

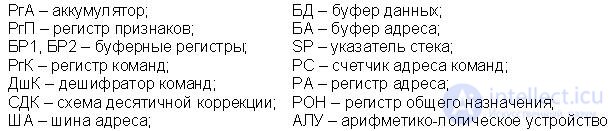

Буферы адреса и данных связывают МП с внешними шинами адреса и данных (шинами системного интерфейса). В качестве выходных каскадов в буферах используются логические элементы с тремя состояниями. Это позволяет процессору отключаться от внешних шин и предоставлять их в распоряжение ПУ. Буфер ШД двунаправленный, что позволяет использовать ШД в полудуплексном режиме для приема и передачи информации в неперекрывающиеся интервалы времени.

Принцип двунаправленного обмена данными между внутренней и внешней ШД можно пояснить схемой, изображенной на рис. 16.3.

Следует помнить, что передача информации по шинам как внутренним, так и внешним осуществляется в параллельном коде, т.е. выходные и входные логические элементы буфера ШД имеют 8- канальную структуру.

Рис.16.3. Функциональная схема буфера ШД МП

С точки зрения пользователя, реализация физических процессов, протекающих в микросхеме, не представляет особого интереса, как и физическая реализация отдельных узлов МП. В распоряжение пользователя предоставляется ряд формальных устройств МП, с которыми он может производить те или иные манипуляции посредством команд программы. Для общения с тем или иным устройством пользователю необходимо знать адрес или номер этого устройства.

Структура МП I8080 (КР580), с точки зрения программиста, представлена на рис. 16.4. Аккумулятор и регистр признаков (флагов) являются половинами одного 16-битного регистра, но пользователь может обращаться к ним как к отдельным 8-битовым регистрам. В документации на МП КР580 содержимое РгП названо словом состояния процессора (PSW). Однако некоторые авторы под PSW понимают не только содержимое РгП, но и содержимое аккумулятора, т.е. PSW ≡ (А)(F). Такая трактовка PSW (регистра PSW) используется при дальнейшем изложении материала.

Таким образом, пользователь имеет в своем распоряжении:

- восьмибитовые регистры A, B, C, D, E, H, L, каждый из которых имеет свой трехразрядный адрес (номер);

- 16-битовые регистровые пары BC, DE, HL, определяемые по имени старшего регистра пары (т.е. B, D, H);

- 16-битовые регистры PC, SP, PSW;

- 8-битовый РгП(F), который можно рассматривать отдельно от PSW;

- однобитовый регистр (триггер) разрешения прерывания.

Рис.16.4. МП с точки зрения программиста

Более подробно РгП (F) изображен на рис. 16.5.

Рис.16.5. Регистр признаков

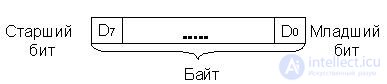

Основной формат данных изображен на рис. 16.6.

Рис.16.6. Основной формат данных

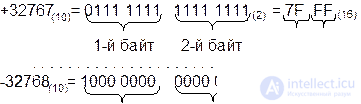

В микропроцессоре байт данных может интерпретироваться следующим образом:

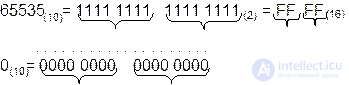

· Целое число без знака

255(10) = 1111 1111(2) = FF(16) (FFH)

. . . . . . . . . . . . . . . .

0(10) = 0000 0000(2) = 00(16) (00H).

· Число со знаком в дополнительном коде

+127(10) = 0111 1111(2) = 7F(16)

. . . . . . . . . . . . . . . .

0(10) = 0000 0000(2) = 00(16)

-1(10) = 1111 1111(2) = FF(16)

. . . . . . . . . . . . . . . .

-128(10) = 1000 0000(2) = 80(16).

· Двухразрядное двоично-десятичное число

99(10) = 1001 1001(2) = 99(16)

. . . . . . . . . . . . . . . .

0(10) = 0000 0000(2) = 00(16).

· Логический байт данных.

В ряде случаев используется двухбайтовый формат данных:

· Двухбайтовое число со знаком в дополнительном коде

· Двухбайтовое число без знака

Для команд используются одно-, двух-, трехбайтовые форматы, причем код операции (КОП) занимает всегда 1 байт. Кроме того, следует помнить, что ША имеет 16 разрядов, т.е. позволяет адресоваться к памяти в 64К однобайтовых ячеек. Следовательно, в этом случае для адреса требуется 2 байта.

В то же время, используя команды INPUT/OUTPUT, программист может адресоваться к 256- регистрам ППУ. Следовательно, в этом случае для адреса требуется только 1 байт, который передается по младшим разрядам ША А7...А0. (Этот же байт дублируется в старших разрядах ША А15...А8, т.е. если адрес регистра F8, то на ША присутствует F8F8).

В общем случае форматы команд МП имеют вид, показанный на рис. 16.7. В первом байте помещается КОП, а во втором однобайтовый операнд или номер регистра ППУ (рис. 16.7, а, б).

Рис.16.7. Форматы команд

В трехбайтовом формате (рис. 16.7, в) первый байт содержит код операции (КОП). Два следующих байта содержат соответственно младший и старший байты адреса ячеек ОП (ПЗУ) либо двухбайтовый операнд.

Способы адресации рассмотрим очень коротко, поскольку все типы адресации в общем виде разобраны ранее.

Прямая адресация

В этом случае источником или приемником операнда являются ячейки памяти или регистр ППУ.

Адрес ячейки памяти или регистра ППУ записывается в команде:

- двухбайтовая команда – адрес регистра ППУ;

- трехбайтовая команда – адрес ячейки памяти.

Регистровая адресация

В этом случае источником или приемником операнда является РОН. Номер РОН записывается в коде операции. Команды однобайтовые (номер РОН – 3 разряда).

Косвенная адресация

В этом случае источником или приемником операнда является ячейка памяти. Командыоднобайтовые. Адрес ячейки памяти находится в регистровой паре, например HL. Есть команды инкремента и декремента (±1) содержимого регистровых пар, что позволяет модифицировать адрес.

Стековая адресация

В этом случае источником или приемником операнда является ячейка памяти. Командыоднобайтовые.

Адрес вершины стека находится в указателе стека SP. При заполнении стек растет в сторону уменьшения адресов, т.е. формируется стек, который ранее был назван перевернутым. Начальный адрес стека устанавливается в указателе стека (SP) программным путем. Уже отмечалось, что SP имеет 16 разрядов, поэтому, если начальным адресом стека выбрать последний адрес всего адресного пространства, то стек может иметь емкость 64 Кбайт.

Обмен со стеком (т.е. загрузка/выгрузка) производится двухбайтовыми словами. При этом загрузка в стек сводится к следующей последовательности действий со стороны МП:

- выполняется операция (SP) = (SP) - 1;

- по новому адресу записывается старший байт вводимого двухбайтового

слова;

- выполняется операция (SP) = (SP) - 1;

- по новому адресу записывается младший байт (второй) вводимого двухбайтового слова.

Выгрузка стека сводится к следующему:

- считывается младший байт по адресу (SP);

- выполняется операция (SP) = (SP) + 1;

- считывается старший байт по новому адресу;

- выполняется операция (SP) = (SP) + 1.

Непосредственная адресация

В этом случае операнд находится в самой команде. Операнд может быть одно- и двухбайтовым. В соответствии с этим команды могут быть двухбайтовыми итрехбайтовыми (первый байт всегда занимает КОП).

Следует помнить, что в трехбайтовой команде младшие разряды 16-битового числа содержатся во втором байте команды, а старшие в третьем.

1. Приведите условное обозначение МП КР580ВМ80. Опишите назначение всех выводов.

2. Функциональная схема МП КР580ВМ80.

3. Назначение отдельных разрядов слова состояния регистра признаков МП КР580ВМ80.

4. Функциональная схема буфера ШД МП КР580ВМ80.

5. МП КР580ВМ80 с точки зрения программиста.

6. Форматы данных и команд в МП КР580ВМ80.

7. Способы адресации в МП КР580ВМ80.

Надеюсь, эта статья про универсальные микропроцессоры, была вам полезна, счастья и удачи в ваших начинаниях! Надеюсь, что теперь ты понял что такое универсальные микропроцессоры, архитектура процессора кр580вм80 и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Компьютерная схемотехника и архитектура компьютеров

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров