Лекция

Привет, сегодня поговорим про структуры микропроцессорных систем, обещаю рассказать все что знаю. Для того чтобы лучше понимать что такое структуры микропроцессорных систем, микропроцессорная система , настоятельно рекомендую прочитать все из категории Компьютерная схемотехника и архитектура компьютеров.

В зависимости от целевого назначения и используемого процессора ЭВМ существенно различаются по своим вычислительным возможностям, размерам, стоимости конструкции. Несмотря на то что принципы функционирования простейших микроЭВМ и мэйнфреймов в общем-то одинаковы, реальные структуры и алгоритмы функционирования даже небольших современных универсальных ЭВМ (таких, как персональный компьютер) очень громоздки и сложны для первоначального понимания. В связи с этими ниже рассматривается гипотетическая машина, обладающая чертами многих простейших микроЭВМ.

По определению, микроЭВМ – это законченная вычислительная система, построенная на базе микропроцессора и размещенная в одной БИС (однокристальная микроЭВМ) или нескольких БИС, установленных на одной плате (одноплатная микроЭВМ). Причем под законченной вычислительной системой следует понимать любое устройство переработки цифровой информации, включающее процессор, память и подсистему ввода/вывода информации, независимо от его целевого назначения, конструктивного исполнения и способов программирования.

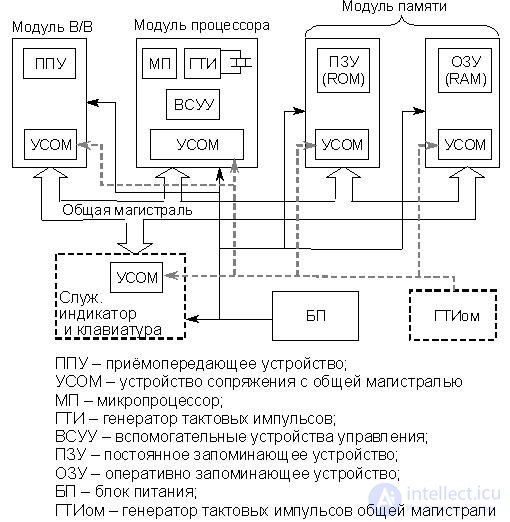

Как уже отмечалось, современные микроЭВМ преимущественно имеют магистрально-модульную структуру. Ее основу в простейшем случае составляет единственная общая магистраль, к которой в необходимой номенклатуре и количестве подключены все устройства ЭВМ, выполненные в виде функционально законченных блоков. При этом все устройства ЭВМ обмениваются друг с другом информацией только через магистраль, используя схожие наборы сигналов и протоколы обмена.

Рассмотрим минимальный набор устройств, который необходим для создания простейшей гипотетической микроЭВМ (рис. 18.1).

Модуль процессора, который включает в себя непосредственно МП, генератор тактовых импульсов (ГТИ) и вспомогательные устройства управления (ВСУУ), внешние по отношению к МП.

· Модули постоянной и оперативной памяти – ПЗУ (ROM) и ОП (RAM) соответственно.

· Модуль ввода/вывода информации (В/В), содержащий приемопередающие устройства (ППУ) для связи с различными периферийными устройствами (ПУ), который может быть также назван модулем адаптеров промежуточных интерфейсов.

· Блок питания (БП).

· В общем случае возможно наличие модуля служебной клавиатуры и дисплея, построенного на семисегментных индикаторах или светодиодах.

Рис.18.1. Обобщенная структура простейшей микро-ЭВМ

Все модули микроЭВМ имеют устройства сопряжения с общей магистралью (УСОМ). Они выполняют ряд важных функций по реализации операций обмена информацией между устройствами микроЭВМ, которые рассматриваются ниже. Следует особо подчеркнуть, что для разных модулей микроЭВМ структуры этих устройств и выполняемые ими функции могут быть существенно различны.

Одной из наиболее простых функций УСОМ является увеличение нагрузочных способностей модулей микроЭВМ и их отдельных устройств, поскольку большинство логических схем, на которых они построены, не могут обеспечить необходимую для передачи по ОМ мощность сигналов.

Кроме того, выходные (входные) каскады блоков УСОМ, присутствующих в каждом модуле микроЭВМ, имеют три устойчивых состояния:

H – высокий уровень (логическая 1);

L – низкий уровень (логический 0);

Z – состояние отключения от шины.

В состоянии Z выходное (входное) сопротивление УСОМ велико (определяется только токами утечек p-n переходов) и соответствующий модуль микроЭВМ может считаться отключенным от магистрали вообще или от ее отдельных линий.

Ранее предполагалось, что все устройства микро-ЭВМ синхронизируются от одного тактового генератора, расположенного в модуле процессора и обозначенного на рис. 18.1 как ГТИ. Однако, как показано на рис. 18.1, УСОМ могут (но не обязательно) синхронизироваться и от отдельного тактового генератора, обозначенного как ГТИом. Индекс «ом» означает, что генератор тактовых импульсов синхронизирует операции обмена по ОМ. Возможна также синхронизация устройств ЭВМ и блоков УСОМ от одного ГТИ. В ряде случаев, как будет показано ниже, синхронизация блоков УСОМ различных модулей микроЭВМ при обмене по ОМ вообще не требуется.

В предыдущих разделах уже были рассмотрены основные принципы функционирования элементарного процессора, взаимодействие его основных частей АЛУ и УУ, а также принципы микропрограммного управления работой процессора. Рассмотрены также основные принципы построения устройств памяти, систем команд микроЭВМ и систем прерывания программ.

Теперь рассмотрим возможные варианты структур микроЭВМ, которые в большой степени определяются структурой ОМ и алгоритмами передачи сигналов по ней между различными блоками, а затем перейдем к рассмотрению непосредственно МП и принципов функционирования простейшей микроЭВМ.

Современные процессоры конструктивно выполняются либо в виде одной БИС (СБИС), либо в виде нескольких БИС, установленных на плате модуля процессора в непосредственной близости друг от друга. Кроме того, на плате модуля процессора обычно размещается также ряд вспомогательных устройств, объединенных на схеме (рис. 14.1) в блок ВСУУ. Такими устройствами могут быть системный контроллер, контроллер прерываний, контроллер прямого доступа, таймеры и т.д. Плата модуля процессора устанавливается на общую магистраль. Это соединение физически может быть реализовано в виде разъема или запаиваемых контактов. В ряде случаев БИС МП устанавливается на магистраль непосредственно.

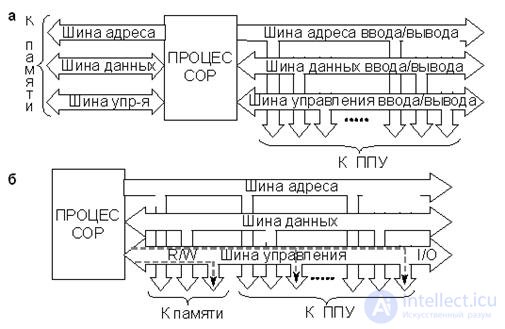

При взаимодействии модуля МП с модулями памяти осуществляются операции считывания или записи информации, а при взаимодействии с ПУ – операции ввода/вывода информации. При этом кроме собственно данных и адресов ячеек памяти или регистров ППУ по магистрали необходимо передавать и весьма большое количество служебных управляющих сигналов. Ввиду этого общую магистраль разделяют на три (в общем случае) самостоятельные шины:

- шину адреса (ША);

- шину данных (ШД);

- шину управления (ШУ).

Технически проще использовать однонаправленные шины, но тогда их число должно увеличиться, т.е. по две шины для операции "Чтение" (Ввод) и "Запись" (Вывод). Это приводит к существенному увеличению числа контактов разъема модуля МП или непосредственно самой БИС МП, а также числа проводников ОМ. Между тем любое увеличение числа проводников ОМ всегда приводит к увеличению стоимости ЭВМ, а в ряде случаев вообще невозможно в силу технических ограничений.

Самым очевидным способом сократить число выводов БИС и проводников ОМ является объединение однонаправленных шин в одну двунаправленную, управляемую соответствующими сигналами – запись/чтение (READ/WRITE) для модулей памяти и ввод/вывод (INPUT/OUTPUT) для модуля ППУ. Ниже рассматриваются 5 вариантов структур ОМ только с двунаправленными шинами.

· Раздельные шины (рис.18.2, а)

Использование отдельных двунаправленных шин упрощает обмен процессора с модулями памяти и ППУ и дает принципиальную возможность вести его в перекрывающиеся интервалы времени. При этом адресные пространства ячеек памяти и регистров ППУ могут перекрываться.

Основным недостатком такой структуры является большое число проводников общей магистрали и контактов модуля МП.

· Изолированные шины (рис.18.2, б)

Сходство процессов обмена процессор – память и процессор – регистры ППУ позволяет использовать в обоих случаях одни и те же проводники ША и ШД.

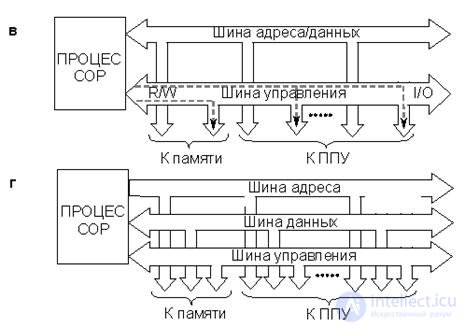

Рис.18.2. Структуры микро-ЭВМ:

а- с раздельными шинами, б – с изолированными шинами,

в – с изолированными шинами и мультиплексированием шин

адресов и данных, г – с общими шинами, д – с общими шинами

и мультиплексированием шин адресов и данных

Это приводит к структуре с изолированными шинами. Адресные пространства ячеек памяти и регистров ППУ, как и при использовании предыдущей структуры, могут перекрываться, т.е. они изолированы. Для того чтобы занять шины для обмена с памятью, процессор выдает сигналы READ/WRITE, а для обмена с ПУ – INPUT/OUTPUT.

По сравнению с предыдущей структурой число проводников ОМ (как и модуля МП) уменьшилось, но исчезла принципиальная возможность вести параллельный обмен с памятью и ПУ.

· Изолированные шины и мультиплексирование ША и ШД (рис. 18.2, в)

В этом случае ША и ШД совмещены. Вследствие этого передача адресов и данных идет в разные моменты времени. Адресные пространства ячеек памяти и регистров ППУ изолированы.

По сравнению с предыдущими структурами уменьшилось число проводников общей магистрали и выводов модуля МП, но адреса и данные могут передаваться только в неперекрывающиеся моменты времени. Это затрудняет возможность конвейеризации процесса выполнения команд и удлиняет цикл обмена процессор – память.

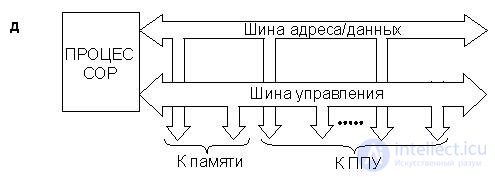

· Общие шины (рис. 18.2, г)

В данном случае команды ввода/вывода (INPUT/OUTPUT) вообще исключены, что упрощает структуру модуля МП и общей магистрали, хотя количество проводников примерно соответствует структуре с изолированными шинами. Ячейки памяти и регистры ППУ лежат в общем адресном пространстве, и для обращения к ним используются одни и те же команды.

В ряде случаев это является преимуществом, однако при возникновении определенных сбоев в работе ПУ и их некорректной обработки со стороны операционной системы возможны "зависания" вычислительного процесса.

· Общие шины и мультиплексирование ША и ШД (рис. 18.2, д)

Недостатки и преимущества данной структуры по сравнению с предыдущей ("общие шины") аналогичны изложенным выше для структуры, приведенной на рис.18.2,в.

Современные МП, практически все, имеют команды ввода/вывода, т.е. дают возможность организовать структуру с изолированными шинами. При этом все они допускают обращение к регистрам ППУ как к ячейкам памяти, т.е. позволяют реализовать структуру с общими шинами.

Следует отметить, что структура магистрали типа "общие шины" является весьма распространенной в реальных устройствах. Понятия "общая магистраль (ОМ)" и "общая шина (ОШ)" в литературе часто используются как синонимы, хотя согласно приведенной выше классификации ОШ является частным случаем структуры ОМ. Ниже, при изложении материала, понятия ОШ и ОМ также будут использоваться как синонимы, за исключением особо оговоренных случаев.

Рассмотренные структуры ОМ во многом определяют внутреннюю структуру конкретной микро-ЭВМ. Однако структура микро-ЭВМ определяется также и множеством вопросов, связанных с формой представления информации и способами ее передачи внутри микро-ЭВМ, алгоритмами взаимодействия отдельных модулей.

Для всесторонней характеристики структуры микро-ЭВМ используют весьма объемное понятие «системный интерфейс», включающее в себя все отмеченные выше вопросы.

Системный интерфейс – это набор цепей, связывающих процессор с памятью и ППУ, алгоритмы передачи сигналов по этим цепям, их электрические и временные параметры, тип соединительных элементов, конструктивные решения и т. Об этом говорит сайт https://intellect.icu . д. (т.е. это комплекс аппаратно-программных средств).

Таким образом, ОМ является важной, но не единственной компонентой системного интерфейса, определяющего структуру микро-ЭВМ в целом.

Необходимо отметить, что в литературе редко используется термин «системный интерфейс» при описании структуры ЭВМ. Обычно используются более короткие термины «шина» или «магистраль».

Существует множество типов системных интерфейсов, разработанных для ЭВМ самых разных назначений. Количество только стандартных системных интерфейсов исчисляется десятками. Полное описание системного интерфейса даже одной, конкретной, ЭВМ далеко выходит за рамки настоящего курса. Между тем необходимо хотя бы коротко остановиться на другой важнейшей компоненте системного интерфейса – алгоритмах передачи сигналов по ОМ. Точнее, на основных принципах построения этих алгоритмов, поскольку они также сильно влияют на внутреннюю структуру и общие характеристики микро-ЭВМ. Для этого необходимо прежде всего ввести понятие «цикл шины».

Как уже отмечалось, в ЭВМ магистрально-модульной архитектуры наличие единого ресурса (магистрали) позволяет вести обмен между устройствами только в не перекрывающиеся моменты времени. Это означает, что в каждый момент времени существует только один канал связи между двумя устройствами, которые могут быть условно названы «передатчик» и «приемник». Возможны различные процедуры обмена по ОМ. Это запись в ОП, считывание из ОП, запись в регистры ППУ, считывание из регистров ППУ, прямой доступ к памяти, а также всевозможные модификации указанных операций. Конкретный протокол, по которому ведется обмен между двумя устройствами ЭВМ, всегда соответствует типу выполняемой процедуры. При выполнении операций обмена УСОМ передатчика выставляет на линии магистрали подлежащую передаче информацию. УСОМ приемника, получив соответствующие управляющие сигналы, должен ее считать. Между моментом установки данных на линиях магистрали и их считыванием возникает некоторый временной интервал, величина которого в общем случае может изменяться. Это обусловлено прежде всего особенностями алгоритма взаимодействия конкретных передатчика и приемника, а также тем, что помимо передачи собственно данных формируется ряд служебных управляющих сигналов, которые необходимы для реализации протокола обмена, причем их количество и номенклатура могут быть различны. Операции блоков УСОМ передатчика и приемника по реализации процедуры обмена могут, но не обязательно, синхронизироваться импульсными последовательностями от ГТИ или ГТИом (в дальнейшем – «синхроимпульсы магистрали»). Синхронизация операций обмена, если она присутствует, может осуществляться как фронтами, так и уровнями синхроимпульсов магистрали. При выполнении различных процедур обмена между устройствами микроЭВМ количество и номенклатура служебных операций, а следовательно, и интервалы времени между операциями установления данных на линиях ОМ и их считыванием могут существенно различаться. Тем более продолжительности операций обмена различаются в микро-ЭВМ, использующих различные типы системных интерфейсов.

Цикл шины (магистрали) – это совокупность служебных операций блоков УСОМ передатчика и приемника, необходимых для реализации конкретной процедуры обмена по ОМ между двумя устройствами ЭВМ.

Для конкретной ОМ существуют различные циклы шины, которые носят соответствующие названия по типам реализуемых процедур обмена. Это шинный цикл чтения регистра ППУ (порта), шинный цикл чтения ячейки памяти, шинный цикл записи в ячейку памяти и т. д.

Длительность цикла шины (магистрали) – это интервал времени, необходимый для реализации конкретной однократной процедуры обмена по ОМ между двумя устройствами ЭВМ. При наличии синхронизации операций обмена этот интервал может измеряться количеством необходимых синхроимпульсов магистрали (количеством тактов шины).

Как уже отмечалось, конкретные количество, номенклатура и последовательность выполнения служебных операций (структура цикла), а также их продолжительность для разных процедур обмена могут существенно различаться. Между тем основные принципыпостроения протоколов различных процедур обмена для конкретной ОМ одинаковы. В общем случае выделяют 4 основных типа протоколов обмена (обычно говорят «типа циклов»), каждый из которых определяет тип ОМ используемой в конкретной ЭВМ и особенности ее внутренней структуры:

синхронный цикл (синхронные магистрали);

асинхронный цикл (асинхронные магистрали);

замкнутый цикл (замкнутые магистрали);

разомкнутый цикл (разомкнутые магистрали).

Рассмотрим перечисленные варианты магистралей несколько подробнее, учитывая тот факт, что данная классификация характеризует принципы функционирования ОМ в разных аспектах. Первые два пункта учитывают наличие синхронизации при выполнении операций обмена. Последние два – наличие информационной обратной связи между передатчиком и приемником. Это означает, что и синхронная, и асинхронная магистраль может быть как замкнутой, так и разомкнутой.

· Синхронные магистрали

Отличительной чертой магистралей этого типа является наличие строгой привязки всех операций по реализации цикла обмена к фронтам или уровням синхроимпульсов магистрали.

Основным преимуществом синхронных магистралей является то, что они имеют более простую логику управляющих устройств блоков УСОМ и обеспечивают наивысшую пропускную способность при обмене. Основным недостатком синхронных магистралей является то, что они требуют комплексную синхронизацию блоков УСОМ, дополнительное оборудование и программное обеспечение, а также примерно одинаковое быстродействие всех устройств магистрали.

· Асинхронные магистрали

Отличительной чертой магистралей этого типа является отсутствие какой-либо синхронизации операций по реализации цикла обмена, т.е. ГТИом отсутствует.

Основным преимуществом асинхронных магистралей является то, что они обладают повышенной гибкостью и позволяют связывать в единую систему устройства ЭВМ, имеющие различное быстродействие. Это свойство оказывается очень важным при построении открытых управляющих систем, например систем АСУ ТП. Основной недостаток асинхронных магистралей в ограниченной пропускной способности при обмене данными. Кроме того, возникает потребность в дополнительных линиях для передачи управляющих сигналов в частности сигнала стробирования.

Очень коротко поясним смысл термина «сигнал стробирования», или просто «строб». При передаче информации по параллельной магистрали всегда существует проблема, связанная с моментом ее считывания. Эта проблема является следствием некоторой электрической асимметрии выходных каскадов УСОМ передатчика и линий ОМ, вызванной технологическими причинами. Указанная асимметрия приводит к разбросу времени установления сигналов на различных линиях ОМ. На синхронных магистралях эта проблема решается за счет введения некоторой задержки операции считывания относительно соответствующего синхроимпульса ОМ. На асинхронных магистралях момент считывания информации приемнику необходимо указывать специальным сигналом – стробом, который поступает из передатчика в приемник по отдельной линии с некоторой фиксированной задержкой относительно момента выставления данных на линиях ОМ.

· Замкнутые магистрали

Отличительной чертой магистралей этого типа является то, что между передатчиком и приемником существует обратная связь, суть которой состоит в следующем. Приемник, после считывания информации с линий ОМ обязан каким-либо сигналом (квитанцией) известить передатчик о завершении цикла обмена. Для передачи квитанции используют либо линии ШД, либо специально выделенные линии. При использовании корректирующих кодов квитанция может сообщить передатчику о возникшей ошибке. Существуют различные алгоритмы обмена по замкнутой магистрали, однако в любом случае передатчик не начинает новый цикл обмена до получения квитанции. При отсутствии квитанции в течение некоторого тайм-аута возникает прерывание, и управление передается операционной системе. Это позволяет предотвратить ошибки в системе, возникающие за счет сбоев в аппаратуре и внешних помех. Последнее особенно важно для аппаратуры промышленного применения, т.е. систем АСУ ТП.

Основным преимуществом замкнутых магистралей является повышенная надежность обмена по ОМ, что существенно повышает надежность вычислительной системы в целом. Основным недостатком замкнутых магистралей является то, что они требуют дополнительное оборудование для формирования и передачи квитанции. Кроме того, несколько увеличивается время цикла обмена из-за тайм-аута при ожидании квитанции.

· Разомкнутые магистрали

Отличительной чертой магистралей этого типа является то, что между передатчиком и приемником не существует никакой обратной связи. Передатчик, выставив на линии ОМ подлежащую передаче информацию, больше «не заботится» о том, считана она приемником или нет. Предполагается, что информация обязательно считана приемником и возможна инициализация нового цикла обмена.

Основным преимуществом разомкнутых магистралей является простота аппаратного и программного обеспечения ОМ, а следовательно, и меньшая стоимость. Кроме того, они имеют повышенную производительность при обмене. Основным недостатком разомкнутых магистралей является повышенная вероятность ошибок в системе, возникающих за счет сбоев в аппаратуре и внешних помех. Это существенно ограничивает область применений разомкнутых магистралей.

Принимая во внимание изложенное, следует отметить, что рассматриваемая ниже микроЭВМ на процессоре КР580ВМ80 построена на простейшем варианте синхронной разомкнутой магистрали. Синхронизация всех устройств и операций обмена по магистрали осуществляется от одного ГТИ.

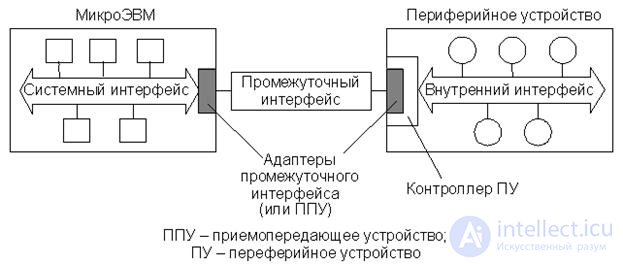

К процессору микроЭВМ обычно подключается достаточно много ПУ. Это клавиатура, индикаторы, печатающие устройства, накопители, различные датчики и исполнительные устройства систем управления и т.д. ПУ свойственны различное быстродействие, различный набор управляющих сигналов, различные электрические параметры, т.е. их внутренний интерфейс (интерфейс ПУ), как правило, не совместим с системным интерфейсом микроЭВМ. Для сопряжения микроЭВМ с ПУ приходится использоватьпромежуточный интерфейс, поддерживаемый с обеих сторон специальнымиадаптерами (ППУ), т.е. между системным интерфейсом микроЭВМ и внутренним интерфейсом ПУ вводится промежуточный интерфейс последовательной или параллельной передачи данных (рис. 18.3). В принципе, каждое ПУ может иметь свой промежуточный интерфейс. Однако для упрощения и унифицирования аппаратуры сопряжения целесообразно использовать единый стандартный промежуточный интерфейс. Используя один и тот же стандартный промежуточный интерфейс последовательной или параллельной передачи данных к микроЭВМ, можно подключать различные ПУ.

Разнообразие ПУ и, прежде всего, их различное быстродействие (например, клавиатура и НМД) не позволяют в реальных микроЭВМ использовать только один тип промежуточного стандартного интерфейса. Между тем каждый из используемых в реальных микроЭВМ стандартных промежуточных интерфейсов позволяет подключать достаточно большие группы ПУ.

Рис.18.3. Включение промежуточного стандартного интерфейса

Существует большое количество стандартных промежуточных интерфейсов, адаптеры которых серийно выпускаются в виде БИС или встроены в БИС МП. В качестве примера можно указать два типа интерфейсов, которые можно назвать классическими – это последовательный интерфейс RS-232C и параллельный интерфейс CENTRONICS. Так, в первом отечественном микропроцессорном комплекте КР580 (прототипом является микропроцессорный комплект фирмы Intel I8080) присутствуют два типа программируемых ППУ – КР580ВВ51 (прототип I8251) и КР580ВВ55 (прототип I8255), являющиеся соответственно адаптерами последовательного и параллельного интерфейсов. Аналогичные ППУ присутствуют и в современных микропроцессорных комплектах. Например, ППУ UPD71051C и UPD71055 фирмы NEC или микросхемы серий 8211 и 8250/1645/16550 и их модификации фирмы Intel.

Наличие стандартного промежуточного интерфейса создает удобство в подключении различных ПУ к микроЭВМ. Однако этого недостаточно для ведения операций обмена с конкретным ПУ. Для каждого ПУ необходима специальная программа, которая, используя стандартный промежуточный интерфейс, будет вести обмен с конкретным ПУ. Такие программы называют драйверами устройств. Обычно они входят в состав операционной системы.

Таким образом, в системах ввода/вывода современных микро-ЭВМ можно выделить, как минимум два уровня сопряжения ПУ с процессором и памятью. На первом уровне ППУ сопрягаются с процессором и памятью через системный интерфейс микро-ЭВМ, который комплексирует отдельные устройства микро-ЭВМ в единую вычислительную систему. На втором уровне сопряжения ППУ микро-ЭВМ посредством шин связи соединяются с аналогичными ППУ соответствующих ПУ, т.е. реализуется стандартный последовательный или параллельный промежуточный интерфейс.

Современные ПУ являются, как правило, сложными функциональными устройствами, для управления которыми одних драйверов устройств оказывается недостаточно. Драйверы могут оказаться недопустимо громоздкими и требовать больших вычислительных затрат со стороны центрального процессора. Кроме того, оперативность управления только через драйвер для быстродействующих ПУ может оказаться недостаточной. В связи с этим в состав сложных ПУ всегда входят специальные устройства управления, называемые контроллеры ПУ.

Следует отметить, что понятие "контроллер ПУ" охватывает очень широкий круг устройств. Контроллеры современных ПУ, таких как видеосистемы, жесткие диски и т.п., представляют собой сложнейшие устройства, имеющие собственные процессоры и память, т.е. являются специализированными микро-ЭВМ с соответствующим программным обеспечением. В то же время контроллером ПУ может быть и достаточно простое устройство, состоящее из нескольких логических схем. В ряде случаев контроллер ПУ может вообще отсутствовать. Тогда работой ПУ полностью управляет драйвер устройства, а сигналы, поступающие через промежуточный интерфейс, непосредственно воздействуют на узлы ПУ. Необходимо иметь в виду, что в функции контроллеров современных сложных ПУ входит не только организация операций обмена с ядром ЭВМ, но и управление функционированием ПУ в целом, например все действия, связанные с организацией системы физических записей на жестком диске.

При наличии контроллера, что характерно для большинства современных ПУ, управляющие сигналы и данные, переданные по промежуточному интерфейсу от микро-ЭВМ, первоначально поступают в контроллер ПУ и подвергаются соответствующей обработке. Это обстоятельство отражено на схеме включения промежуточного интерфейса (рис. 18.3), где адаптер промежуточного интерфейса является как бы частью контроллера ПУ. Передача данных и сигналов состояния от ПУ к микро-ЭВМ также происходит под управлением контроллера ПУ.

Подсистемы ввода/вывода больших ЭВМ имеют гораздо более сложную, многоуровневую иерархическую структуру интерфейсов, управляемую специализированными канальными процессорами. Подобные подсистемы обеспечивают обмен данными с множеством сложных устройств, таких как дисковые массивы, графические станции, серверы баз данных, другие ЭВМ, удаленные терминалы и т.п. Их описание выходит далеко за рамки настоящего раздела.

Вводом/выводом (ВВ) называют передачу данных между ядром ЭВМ, включающим в себя процессор и ОП, и периферийными устройствами (ПУ).

Система ВВ – это единственное средство общения ЭВМ с внешним миром. Ее возможности в серийных ЭВМ представляют собой один из важнейших параметров, определяющих выбор машины для конкретного применения.

Несмотря на разнообразие ПУ, в настоящее время разработано несколько стандартных способов их подключения к ЭВМ и программирования ВВ. Существует три режима ВВ:

· Программный ВВ (нефорсированный).

· ВВ по прерыванию (форсированный).

· Прямой доступ к памяти (ПДП).

Реализация ВВ в каждом из этих режимов отличается программно-аппаратными затратами и, самое важное, скоростью выполнения операций обмена и непроизводительными затратами времени процессора. Суть каждого из трех режимов состоит в следующем.

Программный ВВ. Инициирование и управление ВВ осуществляет процессор по командам прикладной программы. ПУ играют пассивную роль и только сигнализируют о своем состоянии, в частности о готовности к операциям ВВ.

ВВ по прерыванию. Операции ВВ инициирует ПУ, генерируя сигнал запроса прерывания, при этом процессор переключается на подпрограмму обслуживания данного ПУ, вызвавшего прерывание. В результате выполнения подпрограммы (обработчика) осуществляется обмен данными. Действия, выполняемые обработчиком, определяются пользователем, а непосредственно операциями ВВ управляет процессор.

Таким образом, как при программном ВВ, так и при ВВ по прерываниям операциями обмена управляет процессор, поэтому очень часто эти два варианта обмена не разделяют и рассматривают их как программный ВВ. В англоязычной литературе – Programmed Input/Output (PIO). Однако в настоящем курсе эти варианты обмена рассматриваются отдельно.

Прямой доступ к памяти. Процессор в передаче данных не участвует. Он отключается от системной магистрали, а все операции обмена данными идут под управлением специального управляющего устройства – контроллера ПДП. Этот режим используется для быстродействующих ПУ, когда пропускной способности процессора недостаточно.

В каждой ЭВМ применяются особые способы ВВ, различные конфигурации схем и типы устройств. Однако для большинства ЭВМ можно выделить следующие общие принципы:

· Передача данных осуществляется по общей системной магистрали (что характерно для микроЭВМ) либо по специальной магистрали ВВ (что характерно для мини- и больших ЭВМ). Иногда отдельная быстродействующая магистраль ВВ выделяется только для обмена в режиме ПДП.

· Подключение ПУ к системному интерфейсу осуществляется с помощью промежуточного интерфейса, поддерживаемого со стороны микро-ЭВМ и ПУ соответствующими адаптерами.

· Операции ВВ инициируются только в случае готовности ПУ к обмену. При наличии нескольких ПУ и обмене в режиме прерывания или ПДП вводится система приоритетов, позволяющая избежать конфликтов. В соответствии с этой системой контроллер прерываний или ПДП среди ПУ, готовых к обмену, в первую очередь обслуживает ПУ с высшим приоритетом.

· Передача данных осуществляется двумя способами:

- отдельными битами, и тогда промежуточный интерфейс называется последовательным;

- полными словами (например, целым байтом), и тогда промежуточный интерфейс называется параллельным.

· Информация, передаваемая в процессе ВВ, подразделяется:

- на собственно данные (обозначим D);

- управляющие данные (обозначим U).

Управляющие данные от процессора называются также командными словами или приказами. Они инициируют действия, не связанные непосредственно с передачей данных (запуск устройства, запрещение прерываний, установка режимов и т.д.).

Управляющие данные от ПУ называются словами состояния. Они содержат информацию об определенных признаках (о готовности устройства к передаче данных, о наличии ошибок при обмене и т.д.). Состояние обычно представляется в декодированной форме – один бит для каждого признака.

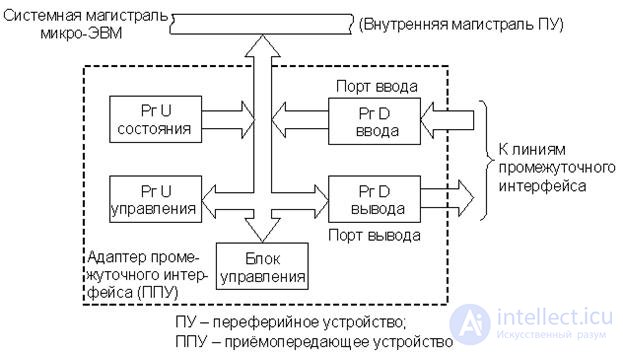

С учетом всего изложенного можно изобразить наиболее общую программную модель адаптера промежуточного интерфейса (ППУ), связывающего системную магистраль микро-ЭВМ и внутреннюю магистраль ПУ. Такая обобщенная программная модель ППУ представлена на рис. 18.4. Каждый из указанных регистров должен иметь адрес, который может идентифицироваться дешифратором адреса.

Рис.18.4. Обобщенная программная модель ППУ

Естественно, что конкретная модель адаптера может отличаться от обобщенной схемы, например, регистр состояния и управления могут быть объединены в один регистр, вместо двух однонаправленных портов используют один двунаправленный, регистров управления может быть несколько. Однако при этом логические функции указанных четырех регистров остаются.

В соответствии с рассмотренными ранее различными структурами системной магистрали возможны два способа организации операций ВВ.

Изолированный ВВ (соответствует структуре с изолированными шинами)

Изолированный ВВ предполагает наличие специальных команд ВВ. В МП КР580 это команды IN и OUT. Адресное пространство регистров ППУ изолировано от адресного пространства ячеек памяти, т.е. регистры ППУ и ячейки памяти могут иметь одинаковый адрес. Команды IN и OUT – двухбайтовые. Первый байт – КОП, а второй несет информацию о номере адресуемого ППУ и номере адресуемого в нем регистра. При этом в МП КР580 предусмотрена возможность обмена данными по командам IN, OUT только между аккумулятором и адресуемыми регистрами.

ВВ по общей шине (соответствует структуре с общими шинами)

В этом случае адресация к регистрам ППУ осуществляется как к обычным ячейкам памяти, т.е. ячейки памяти и регистры ППУ имеют единое адресное пространство. Можно использовать все команды обращения к ячейкам памяти. Это удобно, однако часть адресного пространства памяти используется для адресации регистров ППУ, что может вызвать трудности, если программа большая и много ПУ.

ПУ и микро-ЭВМ могут обмениваться достаточно большими объемами информации, которые невозможно поместить только в регистрах процессора. Ввиду этого часто операции ВВ являются операциями обмена данными между ОП и ПУ. Как уже отмечалось, для повышения гибкости всей вычислительной системы в микро-ЭВМ предусмотрено три режима выполнения операций ВВ.

В режиме программного ВВ все действия, связанные с операциями ВВ, реализуются командами прикладной программы, причем возможны два вида обмена – синхронный и асинхронный, которые целесообразно использовать в различных ситуациях.

Синхронный ВВ

Такой ВВ можно использовать для связи с ПУ, которые "всегда готовы", например светодиодные индикаторы, либо для ПУ, в которых известно точно время выполнения операций, например, максимальное время, необходимое для печати одного знака.

В первом случае команды ВВ ставятся в произвольных точках программы. Во втором случае программа должна быть составлена так, чтобы команды на обмен шли с интервалами не меньшими, чем время выполнения одной операции обмена (т.е. максимальное время выполнения операции в ПУ).

Это наиболее простой вид обмена, требующий минимум программно-аппаратных затрат (он называется еще безусловным ВВ). Однако при работе с медленными ПУ, как правило, не удается оптимальным образом загрузить процессор на период времени между пересылками данных.

Асинхронный ВВ

В этом случае интервал между операциями обмена задается самим ПУ. Информацию о готовности ПУ к операциям обмена процессор получает периодически, анализируя содержимое регистра состояния ППУ, поэтому процесс обмена состоит из двух фаз:

- проверки готовности ПУ к обмену;

- реализации непосредственно операций ВВ.

Первая фаза обмена в большинстве случаев реализуется путем циклического вызова содержимого регистра состояния ППУ в аккумулятор, сравнения его с некоторой маской и анализа полученного результата, т.е. происходит реализация цикла ожидания готовности ПУ. На реализацию цикла ожидания затрачивается время, иногда весьма значительное. Это является существенным недостатком такого вида обмена, поскольку в период ожидания процессор не может выполнять полезной работы, т.е. фактически простаивает.

1. Обобщенная структура простейшей микро-ЭВМ.

2. Структура микро-ЭВМ с раздельными шинами .

3. Структура микро-ЭВМ с изолированными шинами.

4. Структура микро-ЭВМ с изолированными шинами и мультиплексированием шин адресов и данных.

5. Структура микро-ЭВМ с общими шинами.

6. Структура микро-ЭВМ с общими шинами и мультиплексированием шин адресов и данных.

7. Дайте определение длительности цикла шины.

8. Основные типы протоколов обмена по шинам.

9. Включение промежуточного стандартного интерфейса.

10. Режимы ввода/вывода информации в ЭВМ.

11. Обобщенная программная модель приемо-передающего устройства.

Надеюсь, эта статья про структуры микропроцессорных систем, была вам полезна, счастья и удачи в ваших начинаниях! Надеюсь, что теперь ты понял что такое структуры микропроцессорных систем, микропроцессорная система и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Компьютерная схемотехника и архитектура компьютеров

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров