Лекция

Привет, сегодня поговорим про интегрированные системы элементов, обещаю рассказать все что знаю. Для того чтобы лучше понимать что такое интегрированные системы элементов, программируемые логические устройства, плу , настоятельно рекомендую прочитать все из категории Компьютерная схемотехника и архитектура компьютеров.

В предыдущих разделах были изучены наиболее простые цифровые электронные компоненты, выполняющие фиксированные логические функции, так называемая ”рассыпная логика”. Их изучение позволяет перейти к рассмотрению более сложных компонентов, в которых интегрированы от десятков единиц до сотен миллионов простейших элементов. Сюда входят:

- программируемые логические устройства ( плу ),

- программируемые логические интегральные схемы (ПЛИС),

- заказные интегральные схемы (ASIC – application specific integrated circuit)

Наименьшей степенью интеграции отличаются ПЛУ, которые используются для решения небольших и достаточно простых задач. Они могут быть сконфигурированы ( перепрограммированы) пользователем для реализации различных функций. В отличии от них заказные интегральные схемы ASIC могут содержать сотни миллионов простейших логических элементов ( вентилей) и могут выполнять очень сложные функции. Их разработка представляет собой сложный, длительный и дорогостоящий процесс, которым занимаются большие специализированные компании. Поэтому внешним потребителям целесообразно рассматривать только укрупненно их архитектуру и особенности взаимодействия с внешней средой, не вдаваясь в подробности схемотехники отдельных узлов. Основы архитектуры компьютеров, реализуемых в виде ASIC, будут рассмотрены в последующих разделах.

ПЛИС занимают промежуточное положение между ПЛУ и заказными интегральными схемами. С одной стороны, реализуемые ими функции, могут быть оперативно запрограммированы и перепрограммированы на месте самим пользователем. С другой стороны, ПЛИС могут содержать миллионы логических вентилей, что позволяет реализовывать чрезвычайно большие и сложные функции.

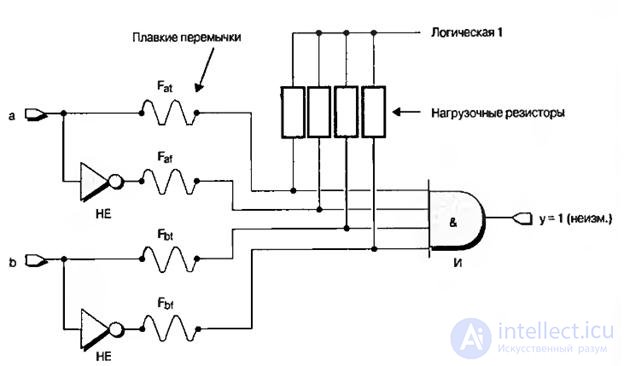

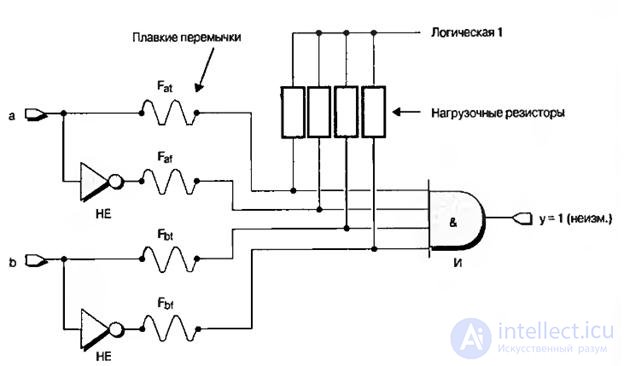

На рис.6.1 приведен пример простой программируемой функции с двумя входами a и b и одним выходом y.

При наличии перемычек на входы схемы совпадения ( операция И) могут подаваться входные сигналы в прямом и инверсном виде. При отсутствии какой-либо перемычки на соответствующий вход схемы совпадения через нагрузочный резистор поступает логическая 1. Различные способы программирования различаются физическими принципами установления перемычек.

Рис.6.1. Простая программируемая функция

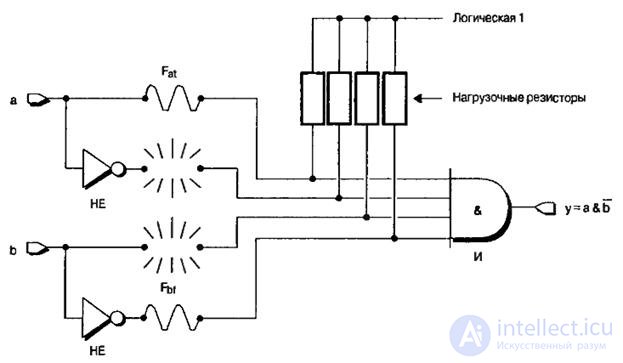

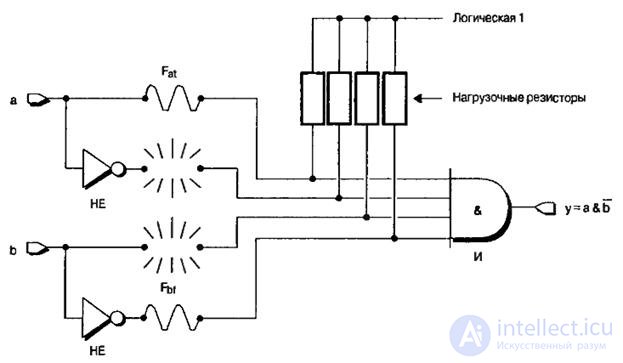

При использовании метода плавких перемычек устройство изготавливается со всеми перемычками (рис.6.2), которые разработчик может выборочно удалять ( прожигать), подавая на входы устройства импульсы относительно высокого напряжения и большого тока. Если, например, удалить из схемы на рис.6.2 перемычки Faf и Fbt ( рис.6.3), то устройство будет формировать функцию

Процесс удаления перемычек называют процессом программирования ( прожигания) устройства. Устройства, конфигурирование которых основано на методе плавких перемычек, являются однократно программируемыми устройствами, так как после прожига плавкая перемычка не может быть восстановлена.

Рис.6.2. Заполнение устройства незапрограммированными плавкими перемычками

Рис.6.3. Плавкие перемычки после программирования

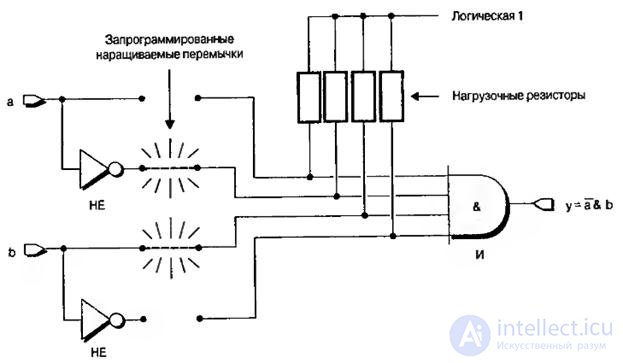

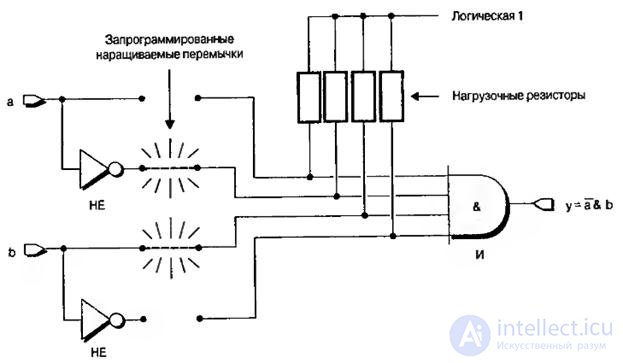

Данный метод прямо противоположен методу плавких перемычек. В незапрограммированном состоянии в устройстве присутствуют все перемычки, но они имеют столь высокое сопротивление, что их можно рассматривать, как разомкнутую цепь. Наращиваемая перемычка первоначально представляет собой микроскопический столбец аморфного ( некристаллического) кремния, связывающего два металлических проводника. Наращивание перемычки ( программирование) осуществляется путем преобразования аморфного кремния-изолятора в токопроводящий поликристаллический кремний с помощью подаваемых на входы устройства импульсов относительно высокого напряжения и большого тока. Например, если нарастить перемычки в цепи инвертированного входа a и прямого входа b, то устройство будет реализовывать функцию ( рис.6.4)

Рис.6.4. Наращиваемые перемычки после программирования

Однажды выращенная перемычка не может быть разрушена или возвращена в исходное состояние. Поэтому устройства, конфигурирование которых основано на методе наращиваемых перемычек являются однократно программируемыми.

Фотошаблоны используются для создания транзисторов и соединяющих их на кремниевом кристалле металлических проводников, которые называются слоями металлизации, а сам процесс программирования еще называют масочным программированием. Рассмотрим, например, транзисторную ячейку постоянного запоминающего устройства (ПЗУ), которая может хранить один бит данных ( рис. 6.5).

Рис.6.5. Транзисторная ячейка ПЗУ, программируемая фотошаблоном

Стандартное устройство ПЗУ состоит из некоторого количества строк

( адреса) и столбцов ( данные), которые вместе образуют массив данных. К каждому столбцу подключен один нагрузочный резистор, который позволяет поддерживать на выводе столбца уровень логической единицы, а в каждом пересечении строки и столбца присутствует транзистор и, при необходимости, перемычка. Наличие/отсутствие перемычки задается фотошаблоном. Программирование ПЗУ с помощью индивидуально изготовленного шаблона состоит в том, что с его помощью определяются ячейки с перемычками и ячейки без перемычек.

При подаче активного сигнала на проводник строки все, подключенные к ней транзисторы, переводятся в открытое состояние. В случае, когда ячейка содержит запрограммированное по фотошаблону соединение, открытый транзистор этой ячейки будет соединять проводник столбца с уровнем логического 0. И наоборот, если в ячейке нет запрограммированного соединения, транзистор не будет вносить какого-либо действия и через нагрузочный резистор, подсоединенный к столбцу, на выход микросхемы будет поступать уровень логической 1.

Масочное программирование используется для программирования ПЗУ и реализации простых логических функций в виде таблиц истинности.

Недостатком устройств, программируемых фотошаблоном, является высокая удельная стоимость производства при малом тираже и неудобство использования при необходимости часто менять конфигурацию компонентов.

В отличие от однократно программируемых устройств, на практике часто бывает удобнее иметь дело с многократно программируемыми

( перепрограммироемыми) устройствами. Одним из вариантов является использование стираемых программируемых постоянных запоминающих устройств (СППЗУ).

СППЗУ-транзистор имеет такую же структуру, как стандартный МОП-транзистор, но с дополнительным ( вторым) плавающим затвором из поликристаллического кремния, изолированного слоями оксида кремния. В незапрограммированном состоянии плавающий затвор не заряжен и не влияет на работу обычного затвора. Чтобы запрограммировать транзистор, необходимо приложить к контактам затвора относительно высокое напряжение, около 12 Вольт. При этом транзистор резко включается, и быстрые электроны преодолевают слой оксида кремния, направляясь в плавающий затвор. После снятия сигнала программирования, отрицательно заряженные частицы остаются в плавающем затворе. Их заряд стабилен и при соблюдении правил эксплуатации не рассеивается на протяжении более 10 лет. Накопленные на плавающем затворе заряды блокируют нормальную работу обычного затвора и, таким образом, позволяют отличать запрограммированные ячейки от незапрограммированных. Благодаря этому свойству такие транзисторы можно использовать для формирования ячеек памяти (рис.6.6).

Рис.6.6. Ячейка памяти на основе СППЗУ-транзистора

Такая ячейка памяти больше не нуждается в плавких перемычках, наращиваемых перемычках или программируемых фотошаблоном соединениях. Для программирования используются входы устройства для заряда плавающих затворов выбранных транзисторов, тем самым блокируя их работу. В этих случаях в ячейках памяти будут храниться логические 1. Стирание ячеек памяти есть не что иное, как ”вытекание” электронов из плавающего затвора, которое происходит под воздействием ультрафиолетового излучения.

Следующая ступенька технологической лестницы представляла собой электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ). В отличие от ячейки СППЗУ, ячейка ЭСППЗУ содержит два транзистора, первый из которых идентичен СППЗУ-транзистору, но имеет очень тонкий изолирующий слой оксида кремния вокруг плавающего затвора. Второй транзистор используется для стирания ячейки памяти электрическим способом.

Технология, известная как Flash, аналогична ЭСППЗУ. Однако, в связи с архитектурными особенностями организации, отдельные ячейки не могут стираться, а только все устройство целиком, либо большими частями.

Определение ”статическое” в названии статического оперативного запоминающего устройства (ОЗУ) отражает тот факт, что однажды записанное в ячейку памяти значение будет оставаться в ней неизменным до тех пор, пока не будет специально изменено или система не будет обесточена. Об этом говорит сайт https://intellect.icu . Обозначение ячейки памяти на основе статического ОЗУ приведено на рис.6.7.

Рис.6.7. Программируемая ячейка памяти на основе статического ОЗУ

Ячейка памяти содержит мультитранзисторный элемент статического ОЗУ, выход которого подключен к дополнительному управляющему транзистору. В зависимости от содержимого ( логический 0 или логическая 1) элемента памяти управляющий транзистор будет закрыт ( то есть отключен) или открыт ( то есть включен). Один из недостатков программируемых устройств на основе ячеек памяти статического ОЗУ состоит в том, что каждая ячейка занимает значительную площадь на поверхности кремниевого кристалла, так как состоит из четырех или шести транзисторов, сконфигурированных в виде регистра-защелки ( регистры, срабатывающие по уровню). Другим недостатком является то, что данные о конфигурации устройства будут утеряны при отключении питания. При включении питания конфигурирование устройства необходимо будет делать заново. Основным достоинством использования ячеек памяти на основе статического ОЗУ является возможность быстро и бесконечное число раз перепрограммировать устройство.

В таблице 6.1 кратко перечислены наиболее важные характеристики рассмотренных технологий проектирования относительно их использования в ПЛИС. Отсутствующая в таблице технология СППЗУ в ПЛИС не используется.

Таблица 6.1. Характеристики технологий программирования

| Характеристика | Статическое ОЗУ | Наращиваемые перемычки | ЭСППЗУ/Flash |

| Технологический процесс | Современ-ный уровень развития | Отставание на од-но или несколько поколений | Отставание на од-но или несколько поколений |

| Перепрограммирование | Да( внутри-системно) | Нет | Да( внутрисистем-но или в выклю-ченном состоянии) |

| Скорость перепрограммиро-вания ( включая стирание) | Быстрая | - | В 3 раза медленнее статического ОЗУ |

| Энергозависимость (возмож-ность программирования при включении питания) | Да | Нет | Нет ( возможно при необходимости) |

| Потребность во внешнем конфигурационном файле | Да | Нет | Нет |

| Пригодность для изготовления прототипов устройств | Да ( высокая пригодность) | Нет | Да ( приемлемо) |

| Готовность к работе сразу после включения питания | Нет | Да | Да |

| Защита прав интеллек-туальной собственности | Приемлемая | Очень хорошая | Очень хорошая |

| Размер конфигурационной ячейки | Большой ( шесть тран-зисторов) | Очень малый | Малый ( два транзистора) |

| Мощность потребления | Средняя | Низкая | Средняя |

| Устойчивость к радиации | Нет | Да | Нет |

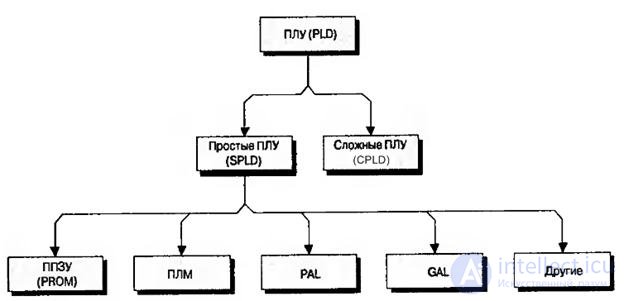

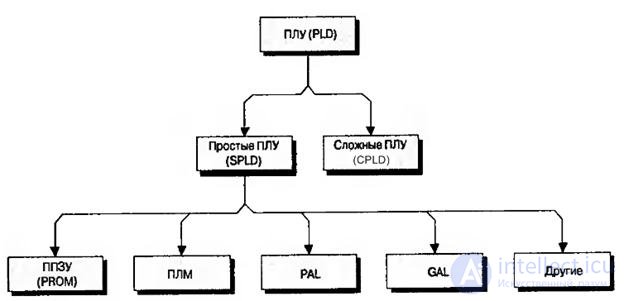

Программируемые логические устройства (ПЛУ) условно подразделяют на простые ПЛУ ( SPLD – simple programmable logic devices) и сложные ПЛУ (CPLD – complex progmmable logic devices), которые, в свою очередь делятся на разновидности в зависимости от используемых технологий программирования ( рис.6.8).

Рис.6.8. Изобилие архитектур ПЛУ

В предыдущих разделах были изучены наиболее простые цифровые электронные компоненты, выполняющие фиксированные логические функции, так называемая ”рассыпная логика”. Их изучение позволяет перейти к рассмотрению более сложных компонентов, в которых интегрированы от десятков единиц до сотен миллионов простейших элементов. Сюда входят:

- программируемые логические устройства (ПЛУ),

- программируемые логические интегральные схемы (ПЛИС),

- заказные интегральные схемы (ASIC – application specific integrated circuit)

Наименьшей степенью интеграции отличаются ПЛУ, которые используются для решения небольших и достаточно простых задач. Они могут быть сконфигурированы ( перепрограммированы) пользователем для реализации различных функций. В отличии от них заказные интегральные схемы ASIC могут содержать сотни миллионов простейших логических элементов ( вентилей) и могут выполнять очень сложные функции. Их разработка представляет собой сложный, длительный и дорогостоящий процесс, которым занимаются большие специализированные компании. Поэтому внешним потребителям целесообразно рассматривать только укрупненно их архитектуру и особенности взаимодействия с внешней средой, не вдаваясь в подробности схемотехники отдельных узлов. Основы архитектуры компьютеров, реализуемых в виде ASIC, будут рассмотрены в последующих разделах.

ПЛИС занимают промежуточное положение между ПЛУ и заказными интегральными схемами. С одной стороны, реализуемые ими функции, могут быть оперативно запрограммированы и перепрограммированы на месте самим пользователем. С другой стороны, ПЛИС могут содержать миллионы логических вентилей, что позволяет реализовывать чрезвычайно большие и сложные функции.

На рис.6.1 приведен пример простой программируемой функции с двумя входами a и b и одним выходом y.

При наличии перемычек на входы схемы совпадения ( операция И) могут подаваться входные сигналы в прямом и инверсном виде. При отсутствии какой-либо перемычки на соответствующий вход схемы совпадения через нагрузочный резистор поступает логическая 1. Различные способы программирования различаются физическими принципами установления перемычек.

Рис.6.1. Простая программируемая функция

При использовании метода плавких перемычек устройство изготавливается со всеми перемычками (рис.6.2), которые разработчик может выборочно удалять ( прожигать), подавая на входы устройства импульсы относительно высокого напряжения и большого тока. Если, например, удалить из схемы на рис.6.2 перемычки Faf и Fbt ( рис.6.3), то устройство будет формировать функцию

Процесс удаления перемычек называют процессом программирования ( прожигания) устройства. Устройства, конфигурирование которых основано на методе плавких перемычек, являются однократно программируемыми устройствами, так как после прожига плавкая перемычка не может быть восстановлена.

Рис.6.2. Заполнение устройства незапрограммированными плавкими перемычками

Рис.6.3. Плавкие перемычки после программирования

Данный метод прямо противоположен методу плавких перемычек. В незапрограммированном состоянии в устройстве присутствуют все перемычки, но они имеют столь высокое сопротивление, что их можно рассматривать, как разомкнутую цепь. Наращиваемая перемычка первоначально представляет собой микроскопический столбец аморфного ( некристаллического) кремния, связывающего два металлических проводника. Наращивание перемычки ( программирование) осуществляется путем преобразования аморфного кремния-изолятора в токопроводящий поликристаллический кремний с помощью подаваемых на входы устройства импульсов относительно высокого напряжения и большого тока. Например, если нарастить перемычки в цепи инвертированного входа a и прямого входа b, то устройство будет реализовывать функцию ( рис.6.4)

Рис.6.4. Наращиваемые перемычки после программирования

Однажды выращенная перемычка не может быть разрушена или возвращена в исходное состояние. Поэтому устройства, конфигурирование которых основано на методе наращиваемых перемычек являются однократно программируемыми.

Фотошаблоны используются для создания транзисторов и соединяющих их на кремниевом кристалле металлических проводников, которые называются слоями металлизации, а сам процесс программирования еще называют масочным программированием. Рассмотрим, например, транзисторную ячейку постоянного запоминающего устройства (ПЗУ), которая может хранить один бит данных ( рис. 6.5).

Рис.6.5. Транзисторная ячейка ПЗУ, программируемая фотошаблоном

Стандартное устройство ПЗУ состоит из некоторого количества строк

( адреса) и столбцов ( данные), которые вместе образуют массив данных. К каждому столбцу подключен один нагрузочный резистор, который позволяет поддерживать на выводе столбца уровень логической единицы, а в каждом пересечении строки и столбца присутствует транзистор и, при необходимости, перемычка. Наличие/отсутствие перемычки задается фотошаблоном. Программирование ПЗУ с помощью индивидуально изготовленного шаблона состоит в том, что с его помощью определяются ячейки с перемычками и ячейки без перемычек.

При подаче активного сигнала на проводник строки все, подключенные к ней транзисторы, переводятся в открытое состояние. В случае, когда ячейка содержит запрограммированное по фотошаблону соединение, открытый транзистор этой ячейки будет соединять проводник столбца с уровнем логического 0. И наоборот, если в ячейке нет запрограммированного соединения, транзистор не будет вносить какого-либо действия и через нагрузочный резистор, подсоединенный к столбцу, на выход микросхемы будет поступать уровень логической 1.

Масочное программирование используется для программирования ПЗУ и реализации простых логических функций в виде таблиц истинности.

Недостатком устройств, программируемых фотошаблоном, является высокая удельная стоимость производства при малом тираже и неудобство использования при необходимости часто менять конфигурацию компонентов.

В отличие от однократно программируемых устройств, на практике часто бывает удобнее иметь дело с многократно программируемыми

( перепрограммироемыми) устройствами. Одним из вариантов является использование стираемых программируемых постоянных запоминающих устройств (СППЗУ).

СППЗУ-транзистор имеет такую же структуру, как стандартный МОП-транзистор, но с дополнительным ( вторым) плавающим затвором из поликристаллического кремния, изолированного слоями оксида кремния. В незапрограммированном состоянии плавающий затвор не заряжен и не влияет на работу обычного затвора. Чтобы запрограммировать транзистор, необходимо приложить к контактам затвора относительно высокое напряжение, около 12 Вольт. При этом транзистор резко включается, и быстрые электроны преодолевают слой оксида кремния, направляясь в плавающий затвор. После снятия сигнала программирования, отрицательно заряженные частицы остаются в плавающем затворе. Их заряд стабилен и при соблюдении правил эксплуатации не рассеивается на протяжении более 10 лет. Накопленные на плавающем затворе заряды блокируют нормальную работу обычного затвора и, таким образом, позволяют отличать запрограммированные ячейки от незапрограммированных. Благодаря этому свойству такие транзисторы можно использовать для формирования ячеек памяти (рис.6.6).

Рис.6.6. Ячейка памяти на основе СППЗУ-транзистора

Такая ячейка памяти больше не нуждается в плавких перемычках, наращиваемых перемычках или программируемых фотошаблоном соединениях. Для программирования используются входы устройства для заряда плавающих затворов выбранных транзисторов, тем самым блокируя их работу. В этих случаях в ячейках памяти будут храниться логические 1. Стирание ячеек памяти есть не что иное, как ”вытекание” электронов из плавающего затвора, которое происходит под воздействием ультрафиолетового излучения.

Следующая ступенька технологической лестницы представляла собой электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ). В отличие от ячейки СППЗУ, ячейка ЭСППЗУ содержит два транзистора, первый из которых идентичен СППЗУ-транзистору, но имеет очень тонкий изолирующий слой оксида кремния вокруг плавающего затвора. Второй транзистор используется для стирания ячейки памяти электрическим способом.

Технология, известная как Flash, аналогична ЭСППЗУ. Однако, в связи с архитектурными особенностями организации, отдельные ячейки не могут стираться, а только все устройство целиком, либо большими частями.

Определение ”статическое” в названии статического оперативного запоминающего устройства (ОЗУ) отражает тот факт, что однажды записанное в ячейку памяти значение будет оставаться в ней неизменным до тех пор, пока не будет специально изменено или система не будет обесточена. Обозначение ячейки памяти на основе статического ОЗУ приведено на рис.6.7.

Рис.6.7. Программируемая ячейка памяти на основе статического ОЗУ

Ячейка памяти содержит мультитранзисторный элемент статического ОЗУ, выход которого подключен к дополнительному управляющему транзистору. В зависимости от содержимого ( логический 0 или логическая 1) элемента памяти управляющий транзистор будет закрыт ( то есть отключен) или открыт ( то есть включен). Один из недостатков программируемых устройств на основе ячеек памяти статического ОЗУ состоит в том, что каждая ячейка занимает значительную площадь на поверхности кремниевого кристалла, так как состоит из четырех или шести транзисторов, сконфигурированных в виде регистра-защелки ( регистры, срабатывающие по уровню). Другим недостатком является то, что данные о конфигурации устройства будут утеряны при отключении питания. При включении питания конфигурирование устройства необходимо будет делать заново. Основным достоинством использования ячеек памяти на основе статического ОЗУ является возможность быстро и бесконечное число раз перепрограммировать устройство.

В таблице 6.1 кратко перечислены наиболее важные характеристики рассмотренных технологий проектирования относительно их использования в ПЛИС. Отсутствующая в таблице технология СППЗУ в ПЛИС не используется.

Таблица 6.1. Характеристики технологий программирования

| Характеристика | Статическое ОЗУ | Наращиваемые перемычки | ЭСППЗУ/Flash |

| Технологический процесс | Современ-ный уровень развития | Отставание на од-но или несколько поколений | Отставание на од-но или несколько поколений |

| Перепрограммирование | Да( внутри-системно) | Нет | Да( внутрисистем-но или в выклю-ченном состоянии) |

| Скорость перепрограммиро-вания ( включая стирание) | Быстрая | - | В 3 раза медленнее статического ОЗУ |

| Энергозависимость (возмож-ность программирования при включении питания) | Да | Нет | Нет ( возможно при необходимости) |

| Потребность во внешнем конфигурационном файле | Да | Нет | Нет |

| Пригодность для изготовления прототипов устройств | Да ( высокая пригодность) | Нет | Да ( приемлемо) |

| Готовность к работе сразу после включения питания | Нет | Да | Да |

| Защита прав интеллек-туальной собственности | Приемлемая | Очень хорошая | Очень хорошая |

| Размер конфигурационной ячейки | Большой ( шесть тран-зисторов) | Очень малый | Малый ( два транзистора) |

| Мощность потребления | Средняя | Низкая | Средняя |

| Устойчивость к радиации | Нет | Да | Нет |

Программируемые логические устройства (ПЛУ) условно подразделяют на простые ПЛУ ( SPLD – simple programmable logic devices) и сложные ПЛУ (CPLD – complex progmmable logic devices), которые, в свою очередь делятся на разновидности в зависимости от используемых технологий программирования ( рис.6.8).

Рис.6.8. Изобилие архитектур ПЛУ

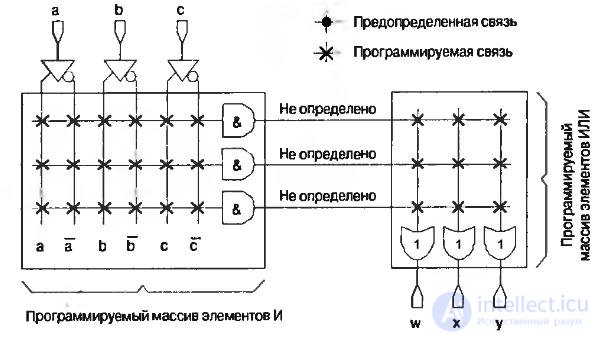

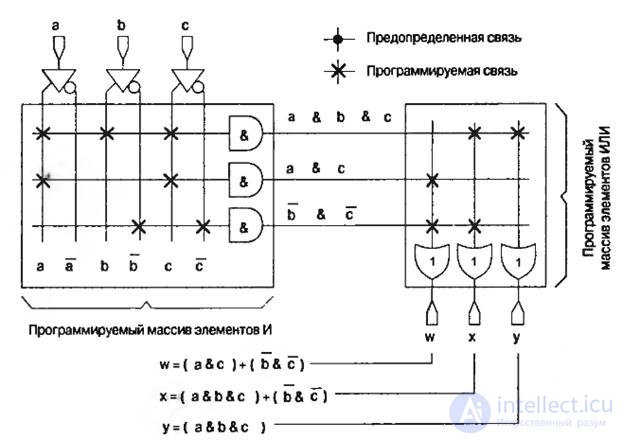

Для примера на рис.6.12 приведена незапрограммированная ПЛМ на три входа и три выхода, а на рис.6.13 показана запрограммированная ПЛМ, реализующая следующие три уравнения :

Рис.6.12. Незапрограммированная ПЛМ

Наряду с преимуществами, которые имеют ПЛМ по сравнению с ППЗУ, у них есть и недостатки. Сигналам для прохождения через программируемые связи требуется больше времени, чем через предопределенные аналоги. Поэтому ПЛМ работает медленнее, чем ППЗУ, так как оба массива и функций И и функций ИЛИ являются программируемыми.

Рис.6.13. Запрограммированная ПЛМ

Для того, чтобы решить проблему быстродействия, свойственную ПЛМ, в конце 1970-х появился новый класс устройств, называемый программируемый массив логики (ПМЛ или PAL – Programmable Array Logic). В отличие от ППЗУ они состоят из программируемого массива логических функций И и предопределенного массива функций ИЛИ. Устройства GAL ( Generic Array Logic – изменяемый массив логики), разработанные в 1983 году компанией Lattice Semiconductor Corporation, представляют собой более сложные электрически стираемые КМОП-разновидности идеологии PAL.

В качестве примера на рис.6.14 приведено простое PAL-устройство с тремя входами и тремя выходами. Преимуществом микросхем PAL по сравнению с ПЛМ является более высокое быстродействие, так как из двух массивов у них только один является программируемым.

Рис.6.14. Незапрограммированное устройство PAL

В отличие от рассмотренных выше примеров микросхем ПЛМ и PAL, промышленность выпускает очень большие ПЛМ и PAL с множеством входов, выходов и с внутренними сигналами. В них могут быть предусмотрены дополнительные программируемые опции, такие, как возможность инвертировать выходы, либо иметь выходы с тремя состояниями, либо и то и другое. Кроме того, некоторые из них поддерживают регистровые выходы и позволят пользователю выбрать версию выхода – регистровую или нерегистровую. Некоторые устройства позволяют конфигурировать определенные выводы в качестве либо выходов, либо дополнительных входов. Этим списком не ограничивается список дополнительных опций, который постоянно пополняется разными производителями.

В начале 1980-х были разработаны более сложные программируемые логические устройства, так называемые сложные ПЛУ (CPLD – complex PLD). Они отличались от простых ПЛУ большей функциональностью, меньшими физическими размерами, более высоким быстродействием и меньшей стоимостью.

Существенный технологический прорыв в этом направлении совершила компания Altera, которая представила сложное ПЛУ, основанное на сочетании КМОП- и СППЗУ-технологий., и в котором использовался центральный коммутационный массив с количеством соединений с входами/выходами блоков менее 100%. Это осложнило программное обеспечение для проектирования ПЛУ, но позволило существенно увеличить быстродействие и значительно снизить потребляемую мощность и стоимость этих устройств.

Несмотря на то, что каждый производитель сложных ПЛУ реализовывал свои уникальные технологии, в общем случае устройство состояло из нескольких блоков простыл ПЛУ, обычно PAL, объединенных общей программируемой коммутационной матрицей ( рис.6.15). Помимо отдельных блоков простых ПЛУ можно было также запрограммировать соединения между ними с помощью программируемой коммутационной матрицы.

Рис.6.15. Общая структура сложного ПЛУ

На рис.6.15 не показаны различные дополнительные компоненты и он дает лишь поверхностное представление о работе сложного ПЛУ. Все структуры сформированы на одном кристалле кремния. Например, программируемая коммутационная матрица может содержать большое количество проводников, скажем 100. Но это больше, чем может быть подключено к блоку простого ПЛУ, который способен работать только с ограниченным количеством сигналов, скажем 30. Блоки простых ПЛУ связаны с коммутационной матрицей своего рода программируемыми мультиплексорами ( рис.6.16).

Рис.6.16. Использование программируемых мультиплексоров

В зависимости от производителя и от типа устройства программируемые переключатели сложных ПЛУ могут быть выполнены на ячейках памяти типа СППЗУ, ЭСППЗУ, Flash или на статическом ОЗУ. При использовании статического ОЗУ появляется возможность увеличить универсальность этой памяти, используя ее в качестве программируемых переключателей и в качестве фактической оперативной памяти.

1. Дайте пример простой программируемой функции.

2. Опишите метод плавких перемычек.

3. Опишите метод наращиваемых перемычек.

4. Принцип программирования устройств фотошаблоном.

5. Опишите ячейку памяти на основе СППЗУ-транзистора.

6. Нарисуйте примеры незапрограммированной и запрограммированной схем ППЗУ.

7. Нарисуйте примеры незапрограммированной и запрограммированной схем ПЛМ.

Надеюсь, эта статья про интегрированные системы элементов, была вам полезна, счастья и удачи в ваших начинаниях! Надеюсь, что теперь ты понял что такое интегрированные системы элементов, программируемые логические устройства, плу и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Компьютерная схемотехника и архитектура компьютеров

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров