Лекция

Привет, сегодня поговорим про программируемые логические интегральные схемы, обещаю рассказать все что знаю. Для того чтобы лучше понимать что такое программируемые логические интегральные схемы, плис , настоятельно рекомендую прочитать все из категории Компьютерная схемотехника и архитектура компьютеров.

FPGA ( field programmable gate arrays) или плис ( программируемые логические интегральные схемы ) представляют собой цифровые интегральные микросхемы (ИС), состоящие из программируемых логических блоков и программируемых соединений между этими блоками.

В зависимости от способа изготовления ПЛИС могут программироваться либо один раз, либо многократно. Устройства,которые могут программироваться только один раз, называются однократно программируемыми.

Словосочетание ”field programmable”, содержащееся в расшифровке аббревиатуры FPGA, означает, что программирование FPGA-устройств выполняется на месте, ”в полевых условиях”, в отличие от устройств, внутренняя функциональность которых жестко прописана производителем. Более того, речь может идти и о возможности модификации функций устройства, встроенного в электронную схему, которая уже как-то используется. Если устройство может быть запрограммировано, оставаясь в составе системы более высокого уровня, оно называется внутрисистемно программируемым.

В настоящее время ПЛИС заполняют четыре крупных сегмента рынка : заказные интегральные схемы, цифровая обработка сигналов, системы на основе встраиваемых микроконтроллеров и микросхемы, обеспечивающие физический уровень передачи данных. Кроме того, с появлением ПЛИС возник новый сектор рынка – системы с перестраиваемой архитектурой, или reconfigurable computing (RC).

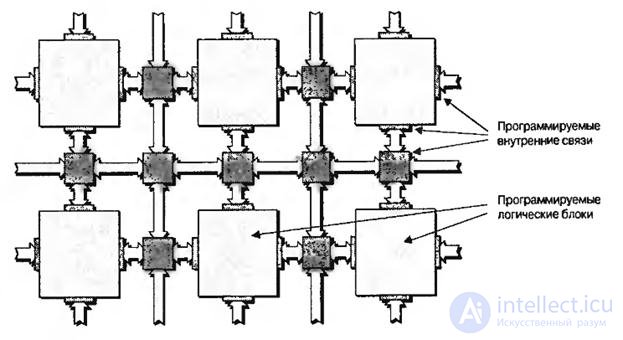

Главной особенностью ПЛИС является их внутренняя структура, которая преимущественно состоит из большого количества простых программируемых логических блоков-”островов” в ”море” программируемых внутренних связей ( рис.7.1).

В мелкомодульной архитектуре каждый логический блок может использоваться для реализации только очень простой функции. Например, блок можно сконфигурировать для работы в качестве 3-входового простого логического элемента ( И, ИЛИ, И-НЕ и так далее) или элемента памяти (триггер D-типа, защелка D-типа и так далее).

Мелкомодульные структуры используются при реализации связующей логики и неоднородных структур, подобных конечным автоматам. Мелкомодульные структуры также эффективны при реализации систолических алгоритмов ( функции, которые чрезвычайно эффективны за счет реализации массового параллелизма). Эти структуры обладают определенным преимуществом при использовании технологии традиционного логического синтеза, которая базируется на мелкомодульной архитектуре заказных микросхем.

Рис.7.1. Об этом говорит сайт https://intellect.icu . Внутренняя структура ПЛИС

Для ”мелкомодульных” ПЛИС характерно большое количество соединений внутри блоков и между ними. По мере увеличения модульности устройств до среднемодульных и выше количество соединений в блоках уменьшается. Это важное свойство, так как внутренние связи определяют величину подавляющего большинства задержек, связанных с прохождением сигналов через ПЛИС.

В “среднемодульных” ПЛИС каждый логический блок содержит относительно большое количество логики по сравнению с “мелкомодульными” ПЛИС. Так, например, логический блок может содержать четыре 4-входовых таблицы соответствия, четыре мультиплексора, четыре D-триггера, и некоторое количество логики быстрого переноса.

“Крупномодульные” ПЛИС содержат массивы узлов, где каждый узел представляет собой сложный элемент, реализующий алгоритмические функции, такие как, например, быстрое преобразование Фурье или ядро микропроцессора общего назначения.

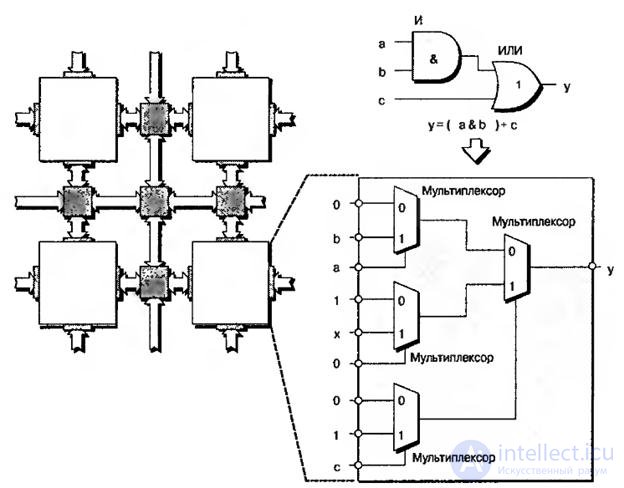

Существуют два основных способа реализации программируемых логических блоков, используемых для формирования среднемодульных устройств: на основе мультиплексоров (MUX – от multiplexer) и на основе таблиц соответствия (LUT –от lookup table).

В качестве примера реализации устройств на основе мультиплексоров рассмотрим 3-входовую функцию y=(a&b)+c, реализованную с помощью блока, содержащего только мультиплексоры (рис.7.2).

Рис.7.2. Логический блок на мультиплексорах

Устройство может быть запрограммировано таким образом, что на каждый его вход может подаваться логический 0 либо логическая 1, либо прямое, либо инвесное значение входного сигнала ( в нашем случае a, b или c), приходящего с другого блока или с входа микросхемы. Такой подход позволяет для каждого блока создавать огромнейшее количество вариантов конфигурирования для выполнения разнообразных функций ( х на входе центрального мультиплексора на рис.7.2 обозначает, что на вход можно подавать любой сигнал – 0 или 1).

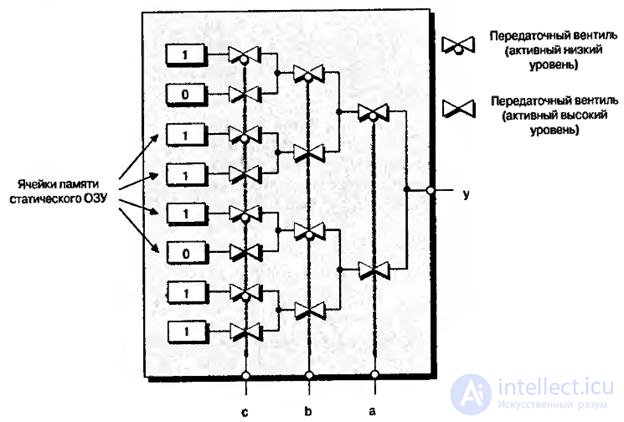

Основная концепция таблиц соответствия проста. В таких микросхемах группа входных сигналов используется в качестве индекса ( указателя, или адреса ячейки) таблицы соответствия. Содержимое этой таблицы организовано таким образом, что ячейки, указываемые каждой входной комбинацией, содержат требуемое выходное значение. Для примера на рис.7.3 приведена схема на логических элементах и ее таблица истинности для функции y=(a&b)+c

Рис.7.3. Требуемая функция и ее таблица истинности

Для реализации этой функции надо загрузить 3-входовую таблицу соответствующими значениями. А теперь допустим, что таблица соответствий формируется из ячеек памяти статического ОЗУ ( она может также быть сформирована наращиваемыми перемычками, ЭСППЗУ- или Flash-ячейками памяти). Для выбора требуемой ячейки ОЗУ с помощью каскада передаточных вентилей используются входные сигналы, как показано на рис.7.4. При этом ячейки памяти статического ОЗУ для загрузки конфигурационных данных должны быть соединены в длинную цепочку, но эти цепи не показаны на рис.7.4 с целью его упрощения.

На схеме открытый, или активный, передаточный вентиль пропускает сигнал с входа на выход. Закрытый вентиль электрически отключает свой выход от проводника, к которому он подсоединен. Передаточные вентили, на обозначениях которых изображен небольшой “кружок”, активизируются при подаче на управляющий вход логического 0. И наоборот, вентили, на обозначениях которых нет кружка, активизируются при подаче на управляющий вход уровня логической 1. Основываясь на этом, легко проследить, как различные входные комбинации могут использоваться для выбора содержимого требуемой ячейки памяти.

Рис.7.4. Таблица соответствия на основе передаточных вентилей

Архитектуры на основе мультиплексоров, в отличие от блоков на основе таблиц соответствия, не обеспечивают работу высокоскоростных цепочек логического переноса. Поэтому большинство современных архитектур ПЛИС реализовывается на основе таблиц соответствия.

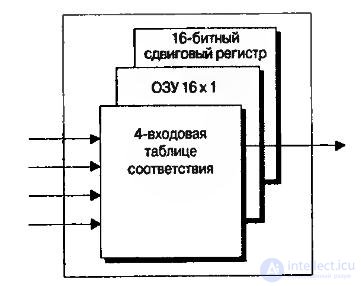

Ядро таблицы соответствия в устройстве на статическом ОЗУ использует для своей работы несколько ячеек памяти. Это позволяет использовать некоторые интересные возможности. Помимо основного назначения, то есть формирования таблицы соответствия, устройства некоторых поставщиков позволяют использовать ячейки, формирующие таблицу, в качестве небольших блоков оперативной памяти. Например, 16 ячеек памяти, формирующих 4-входовую таблицу, могут выступать в роли блока ОЗУ 16•1. Такие участки памяти называются распределенным ОЗУ, так как, во-первых, таблицы соответствия разбросаны ( распределены) по всей поверхности кристалла, а во-вторых, это название отличает их от больших блоков ОЗУ.

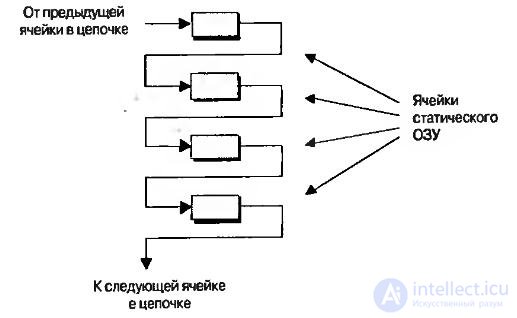

Другой вариант альтернативного использования таблиц основан на том, что все конфигурационные ячейки, включая и те, которые формируют таблицу соответствия, эффективно связаны вместе в одну длинную цепочку (рис.7.5).

Рис.7.5. Конфигурационные ячейки, связанные в цепочку

Дело в том, что в некоторых устройствах ячейки памяти, формирующие таблицу соответствия, после программирования могут рассматриваться независимо от главной структуры цепочки и использоваться в качестве сдвигового регистра. Таким образом, каждую таблицу соответствия можно рассматривать как многофункциональный компонент (рис.7.6).

Рис.7.6. Многофункциональная таблица соответствия

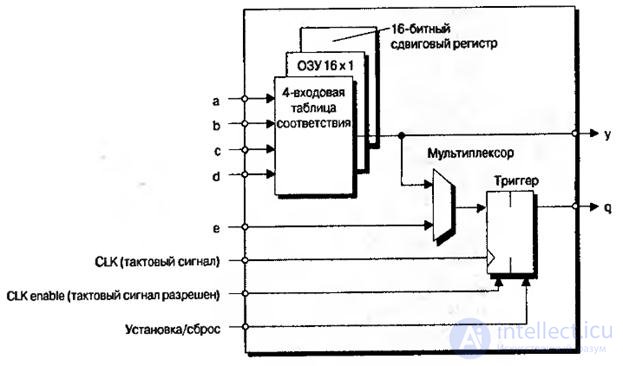

У разных производителей логические блоки могут называться по разному, что не меняет их сути. В ПЛИС фирмы Xilinx блоки называются логическими ячейками (logic cell). Кроме всего прочего, логическая ячейка содержит 4-входовую таблицу соответствия, которая может работать как ОЗУ 16•1 или как 16-битный сдвигающий регистр, а также мультиплексор и регистр (рис.7.5).

Рис.7.5. Упрощенный вид логической ячейки фирмы Xilinx

Полярность тактового сигнала ( реакция триггера на фронт или спад синхроимпульса) может задаваться программно, так же как полярность сигналов “тактовый сигнал разрешен” и “установка/сброс” ( активный высокий или низкий уровень).

Кроме таблиц соответствия, мультиплексоров и регистров, логические ячейки содержат небольшое количество других элементов, включая логику быстрого переноса для использования в арифметических действиях.

Логические блоки, из которых состоят ПЛИС компании Altera, называются логическими элементами ( logic element). Между логическими ячейками Xilinx и логическими элементами Altera существует ряд отличий, но в целом их концепции очень похожи.

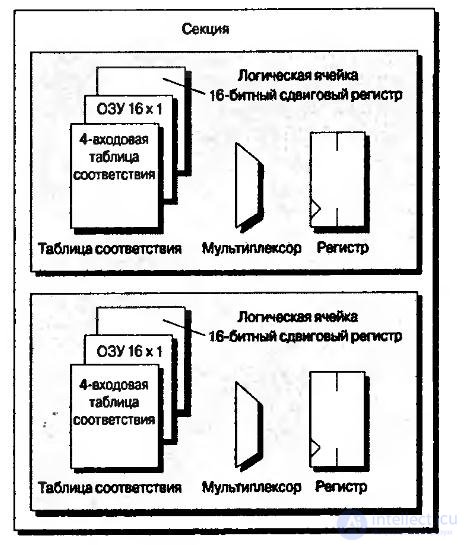

Следующей ступенью в иерархии построения микросхем программируемой логики является, так называемая по определению фирмы Xilinx, секция (slice). На рис.7.6 приведена секция из двух логических ячеек.

Рис.7.6. Секция, содержащая две логические ячейки

На рис.7.6 для упрощения не показаны внутренние связи, также необходимо заметить, что хотя таблицы соответствия, мультиплексоры и регистры каждой ячейки имеют собственные входы и выходы данных, секция имеет общие тактовые сигналы, разрешения тактовых сигналов и установки/сброса для обеих логических ячеек.

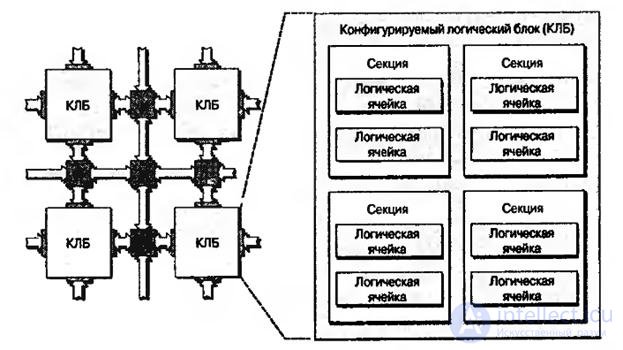

Поднимаясь по иерархической лестнице, мы достигаем уровня, который компания Xilinx называет конфигурируемым логическим блоком КЛБ (CLB – configurable logic block). Компания Altera, в свою очередь, называет его блоком логических массивов или LAB ( logic array block). Другие поставщики ПЛИС дают им свои эквивалентные названия.

Конфигурируемые логические блоки внутри ПЛИС можно представить в виде ”островов” программируемой логики в ”море” программируемых соединений ( рис.7.7).

Рис.7.7. Часть внутренней структуры ПЛИС, содержащая четыре КЛБ, каждый из которых содержит четыре секции

Внутри КЛБ находятся быстрые программируемые внутренние соединения, которые используются для связи между соседними секциями.

Причина существования такой логико-блочной иерархии, то есть логическая ячейка → секция с несколькими ячейками → конфигурируемый логический блок с несколькими секциями, заключается в том, что она дополняется эквивалентной иерархией внутренних соединений. Другими словами, существуют быстрые внутренние соединения между логическими ячейками внутри секции, затем менее быстрые соединения между секциями в конфигурироемом логическом блоке ( КЛБ) и соединения между КЛБ. Подобная иерархия отражает пошаговое достижение оптимального компромисса между простотой соединения внутренних структур и чрезмерными задержками сигналов на внутренних соединениях.

Как уже отмечалось, каждая 4-входовая таблица соответствия может использоваться в качестве блока ОЗУ 16•1. В четырехсекционном КЛБ, приведенном на рис.7.7, все таблицы соответствия внутри этого блока могут быть сконфигурированы для реализации следующих функций:

· Однопортовый блок ОЗУ 16•8 бит.

· Однопортовый блок ОЗУ 32•4 бит.

· Однопортовый блок ОЗУ 64•2 бит.

· Однопортовый блок ОЗУ 128•1 бит.

· Двухпортовый блок ОЗУ 16•4 бита.

· Двухпортовый блок ОЗУ 32•2 бита.

· Двухпортовый блок ОЗУ 64•1 бит.

Портом обычно называют набор сигналов управления и данных, рассматриваемых, как единое целое. В однопортовом ОЗУ данные записываются и считываются из ячейки через общую шину данных. В двухпортовом ОЗУ данные записываются и считываются через различные шины ( порты). На практике в этом случае операции чтения и записи, как правило, работают со своими адресными шинами ( используемыми для указания необходимой ячейки внутри ОЗУ), то есть операции чтения и записи в двухпортовом ОЗУ могут выполняться одновременно.

Аналогично, каждая 4-битовая таблица соответствий может использоваться в качестве 16-битного сдвигового регистра. Для этого существуют специальные соединения между логическими ячейками внутри секции и между секциями, которые позволяют соединить последний бит одного сдвигового регистра с первым битом другого регистра без привлечения к этому процессу выходных сигналов таблиц соответствия. Последние также могут использоваться для просмотра содержимого определенного бита в 16-битном регистре. Это позволяет, при необходимости, соединить вместе таблицы соответствия внутри одного КЛБ и реализовать длинный сдвиговый регистр ( для КЛБ на рис.7.7 длина регистра будет 128 бит).

1. Перечислите сегменты рынка, где присутствуют ПЛИС.

2. Нарисуйте обобщенный пример внутренней структуры ПЛИС.

3. Опишите логические блоки на мультиплексорах и их отличие от блоков на основе таблиц соответствия.

4. Таблица соответствия на основе передаточных вентилей.

5. Нарисуйте упрощенный вид логической ячейки фирмы Xilinx и опишите назначение всех сигналов.

Надеюсь, эта статья про программируемые логические интегральные схемы, была вам полезна, счастья и удачи в ваших начинаниях! Надеюсь, что теперь ты понял что такое программируемые логические интегральные схемы, плис и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Компьютерная схемотехника и архитектура компьютеров

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров