Лекция

Привет, сегодня поговорим про risk, обещаю рассказать все что знаю. Для того чтобы лучше понимать что такое risk, arm , настоятельно рекомендую прочитать все из категории Компьютерная схемотехника и архитектура компьютеров.

Развитие архитектуры компьютеров, направленное на повышение их производительности, в последние десятилетия шло по пути усложнения процессоров путем расширения системы команд, введения сложных команд, выполняющих процедуры, приближающиеся к примитивам языков высокого уровня, увеличения числа используемых способов адресации и т.д.

Однако расширение и усложнение набора команд порождает и ряд нежелательных побочных эффектов. Расширение набора команд, числа способов адресации, введение сложных команд сопровождается увеличением длины команды и, в первую очередь, кода операции, что ведет к увеличению числа форматов команд. Это вызывает усложнение и замедление процесса дешифрации кода операции и других процедур обработки команд в процессоре. Возрастающая сложность процедур обработки команд заставляет использовать микропрограммные управляющие устройства с управляющей памятью (микропрограммные УУ) вместо более быстродействующих УУ с жесткой логикой. Усложнение процессора делает более трудным и даже невыполнимым реализацию его на одном кристалле БИС. А размещение процессора в одном кристалле за счет сокращения длин межсоединений облегчает достижение высокой производительности.

Сказанное выше объясняет, почему в начале 80-х гг. сформировалось альтернативное по отношению к усложнению архитектуры процессоров направление. При создании относительно дешевых высокопроизводительных ЭВМ оно использует архитектуру с сокращенным набором команд (СНК-архитектура), называемую в зарубежной литературе RISC-архитектурой. Ниже рассматриваются только основные принципы, заложенные в основу классической RISC-архитектуры.

RISC-архитектура предполагает реализацию в ЭВМ сокращенного набора простейших, но часто употребляемых команд. Это позволяет упростить аппаратные средства процессора и получить возможность повысить его быстродействие. При использовании RISC-архитектуры выбор набора команд и структуры процессора направлены на то, чтобы команды набора выполнялись за один машинный цикл процессора. Выполнение более сложных, но редко встречаемых операций обеспечивают подпрограммы.

В RISC-компьютер машинным циклом называется время, в течение которого производится выборка двух операндов из регистров, выполнение операции в АЛУ и запоминание результатов в регистре. Большинство команд в RISC являются быстрыми командами типа "регистр-регистр" и выполняются без обращения к ОП. Для того, чтобы это было возможно, процессор должен содержать достаточно большое число общих регистров.

Таким образом, ЭВМ RISC-архитектуры имеют ряд характерных особенностей:

Все это упрощает УУ процессора и позволяет обходиться без микропрограммного уровня управления и управляющей памяти, т.е. УУ может быть выполнено на быстродействующей жесткой логике.

Рассмотренные выше особенности, присущие компьютерам RISC-архитектуры, приводят к столь значительному упрощению процессора, что возникает возможность размещения в одном кристалле не только процессора, но и большого количества общих регистров. В современных БИС МП RISC-архитектуры число общих и специализированных регистров достигает десятков и сотен при существенном сокращении общего числа транзисторов процессора. Так, например, для реализации 32-разрядных процессоров RISC-архитектуры, соответствующих производительности процессоров класса I80386, требуется менее 50000 транзисторов, в то время как для процессоров традиционной архитектуры (CISC) – более 150 000.

Большое число РОН, особенно при наличии обеспечивающего их эффективное использование "оптимизирующего компилятора", позволяет до предела сократить обращение к ОП. Это достигается:

Одной из характерных особенностей RISC-архитектуры является широкое использование механизма перекрывающихся регистровых окон. Он предназначен для уменьшения числа обращений к ОП и межрегистровых передач, что способствует повышению производительности ЭВМ.

Процедурам динамически выделяются небольшие группы регистров фиксированной длины (регистровые окна). Окна последовательно выполняемых процедур перекрываются, благодаря чему возможна передача параметров от одной процедуры к другой. При вызове процедуры процессор переключается на работу с другим регистровым окном. При этом не возникает необходимость в передаче содержимого регистров в память.

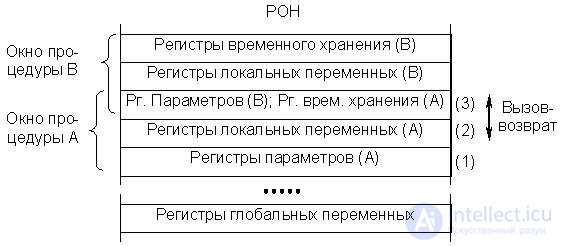

Окно состоит из трех подгрупп регистров (рис. 24.1).

Рис.24.1. RISK – архитектура ЭВМ. Перекрывающиеся регистровые окна

Полагаем, что вызов процедур идет снизу вверх, т.е. процедура A вызывает процедуру B, причем сама была вызвана некоторой предшествующей процедурой. Первая подгруппа содержит параметры, переданные данной процедуре (A) от ее вызвавшей, и результаты для вызывающей процедуры при возврате в нее. Вторая подгруппа содержит локальные переменные процедуры A. Третья является буфером для двухстороннего обмена между процедурой A и вызываемой ею процедурой B. Процедура A передает B параметры при вызове. При возврате из процедуры B в процедуру A последняя получает через этот буфер результаты работы процедуры B. Таким образом, одна и та же подгруппа для процедуры A является регистрами временного хранения, а для следующей (процедуры B) – регистрами параметров. Отдельное окно, доступное всем процедурам программы, выделяется для ее глобальных переменных.

Следует отметить, что компьютеров, полностью удовлетворяющих определению RISC-архитектуры, относительно немного. В большинстве случаев это компьютеры, близкие к RISC-архитектуре. Например, одним из первых компьютеров такого типа являлся высокопроизводительный РС фирмы IBM PC-RT. Он имел 118 команд, всего два способа адресации и два формата команд, 16 РОН, среднее число циклов на команду – три. К чисто RISC-архитектуре принято относить процессоры серии "Alpha" фирмы DEC, серию процессоров "Power PC" совместной разработки фирм Motorola, EPL, IBM, серию процессоров "Rxxxx" (R4000, R5000, R10000) фирмы Mips, серию процессоров "РА" фирмы Hewlett Packard, серию процессоров "SPARC" фирмы Sun Microsystems и др.

Несмотря на широкое использование в литературе терминов "RISC" и "CISC", архитектуры современных мощных процессоров трудно поддаются однозначной классификации. Это связано со стремительным усложнением кристаллов процессоров обоих типов архитектур (RISC и CISC), а также с тем, что в целях повышения производительности разработчики объединяют конструктивные решения, характерные для обоих типов архитектур, в одном устройстве. Так, в мощных CISC-процессорах стало обычным использование RISC-ядра, которое позволяет выполнять сложные команды процессора как наборы элементарных команд, реализуемых по принципам RISC-архитектуры.

Следует отметить также, что принципы RISC-архитектуры заложены в идеологию построения транспьютеров, составляющих основу современных матричных процессоров, используемых в суперЭВМ, а также в платах-"ускорителях" для персональных компьютеров.

Несмотря на интенсивное использование RISC-архитектуры в серийных образцах ЭВМ, продолжаются споры вокруг достоинств и недостатков этой архитектуры. К последним, в частности, относят большую длину кода программы после компиляции (объектного кода) по сравнению с длиной кода машин обычной архитектуры. Так, при эмуляции команд ЭВМ типа VAX в среднем на каждую его команду требуется 5-6 команд машин RISC-архитектуры. Однако, как показали исследования, выигрыш в скорости выполнения команд перекрывает проигрыш от удлинения объектного кода (в общих показателях качества ЭВМ).

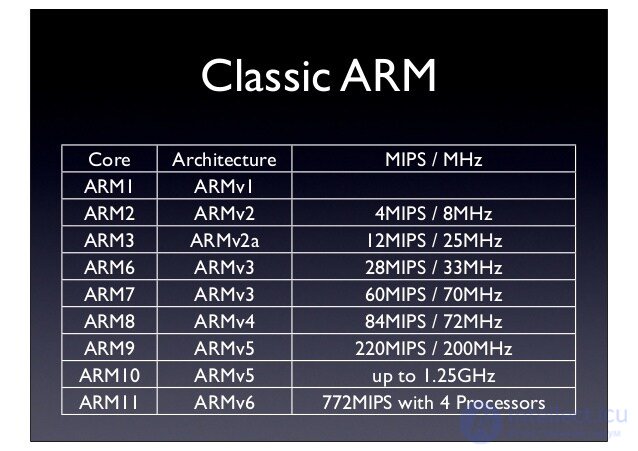

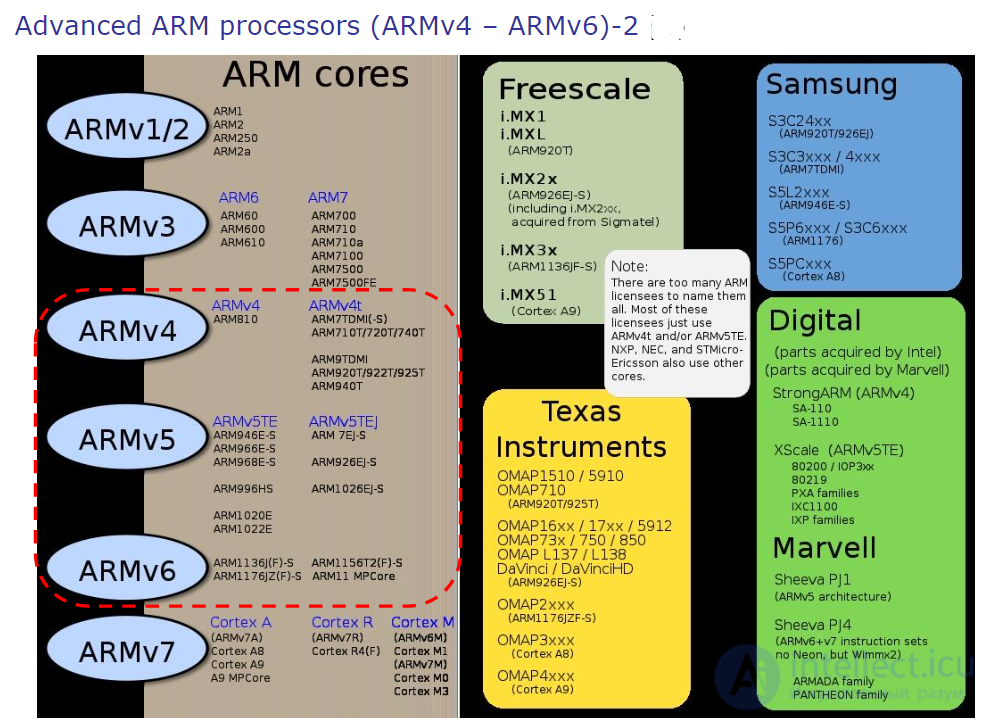

В качестве примера RISK архитектуры рассмотрим ARM процессоры, на долю которых приходится более 90% всех встроенных 32 разрядных RISK процессоров. Эти процессоры имеют низкое потребление и высокую производительность, что определяет их широкое использование в таких устройствах, как КПК ( карманный персональный компьютер), мобильных телефонах, цифровых носителях и плеерах, портативных игровых консолях, калькуляторах и компьютерных периферийных устройствах, таких как жесткие диски или маршрутизаторы.

Процессоры ARM (Advanced RISK Machine – усовершенствованная RISK – машина) разрабатываются британской компанией ARM и ее лицензиатами. Сама компания ARM не занимается выпуском микросхем, а продает готовые решения для процессорного ядра другим компаниям, которые пристраивают к ядру свою периферию и занимаются выпуском микросхем и устройств на их основе.

На данный момент компания ARM выпускает следующие семейства процессоров: ARM7, ARM9, ARM10, ARM11 и Cortex. Объявлено о подготовке к выпуску в 2012 году семейства ARM A15 под кодовым названием Eagle.

Процессоры ARM A15 будут обладать следующими характеристиками: тактовая частота до 2,5 ГГц, одно, два, четыре или восемь ядер, поддержка 1 терабайта оперативной памяти, ECC кеш L1 и L2, общий кеш для многопроцессорных систем, поддержка виртуализации, двойная проверка операций с плавающей запятой, векторные инструкции, слежение за кешем.

В отдельных моделях будущих чипов компании ARM обещает поддержку технологии многопоточности, которая позволит каждому ядру одновременно обрабатывать более одного потока инструкций.

По лицензии компании ARM производят микропроцессоры такие фирмы как Atmel, Cirrus Logic, Intel, Marvell, NXP, STMicroelectronics, Samsung, Qualcomm, Sony Ericsson, Texas Instruments, nVidia, Freescale, Analog Devises и другие. Примеры процессоров разработанных основными лицензиатами: DEC StrongARM, Freescale i.MX, Marvell XScale, NVIDIA Tegra, ST-Ericsson Nomadik, Qualcomm Snapdragon и Texas Instruments OMAP.

А теперь, когда мы рассмотрели историю развития этих архитектур и их принципиальные отличия, давайте сделаем подробное сравнение ARM и x86, по различным их характеристикам, чтобы определить что лучше и более точно понять в чем их разница.

Производство x86 vs arm отличается. Процессоры x86 производят только две компании Intel и AMD. Изначально эта была одна компания, но это совсем другая история. Право на выпуск таких процессоров есть только у этих компаний, а это значит, что и направлением развития инфраструктуры будут управлять только они.

ARM работает совсем по-другому. Компания, разрабатывающая ARM, не выпускает ничего. Они просто выдают разрешение на разработку процессоров этой архитектуры, а уже производители могут делать все, что им нужно, например, выпускать специфические чипы с нужными им модулями.

Это главные различия архитектуры arm и x86. Процессоры x86 развивались стремительно, как более мощные и производительные. Разработчики добавили большое количество инструкций процессора, причем здесь есть не просто базовый набор, а достаточно много команд, без которых можно было бы обойтись. Изначально это делалось чтобы уменьшить объем памяти занимаемый программами на диске. Также было разработано много вариантов защит и виртуализаций, оптимизаций и многое другое. Все это требует дополнительных транзисторов и энергии.

ARM более прост. Здесь намного меньше инструкций процессора, только те, которые нужны операционной системе и реально используются. Если сравнивать x86, то там используется только 30% от всех возможных инструкций. Их проще выучить, если вы решили писать программы вручную, а также для их реализации нужно меньше транзисторов.

Из предыдущего пункта выплывает еще один вывод. Чем больше транзисторов на плате, тем больше ее площадь и потребление энергии, правильно и обратное.

Процессоры x86 потребляют намного больше энергии, чем ARM. Но на потребление энергии также влияет размер самого транзистора. Например, процессор Intel i7 потребляет 47 Ватт, а любой процессор ARM для смартфонов - не более 3 Ватт. Раньше выпускались платы с размером одного элемента 80 нм, затем Intel добилась уменьшения до 22 нм, а в этом году ученые получили возможность создать плату с размером элемента 1 нанометр. Это очень сильно уменьшит энергопотребление без потерь производительности.

За последние годы потребление энергии процессорами x86 очень сильно уменьшилось, например, новые процессоры Intel Haswell могут работать дольше от батареи. Сейчас разница arm vs x86 постепенно стирается.

Количество транзисторов влияет еще на один параметр - это выделение тепла. Современные устройства не могут преобразовывать всю энергию в эффективное действие, часть ее рассеивается в виде тепла. КПД плат одинаковый, а значит чем меньше транзисторов и чем меньше их размер - тем меньше тепла будет выделять процессор. Тут уже не возникает вопрос ARM или x86 будет выделять меньше теплоты.

ARM изначально не были заточены для максимальной производительности, это область преуспевания x86. Отчасти этому причина меньше количество транзисторов. Но в последнее время производительность ARM процессоров растет, и они уже могут полноценно использоваться в ноутбуках или на серверах.

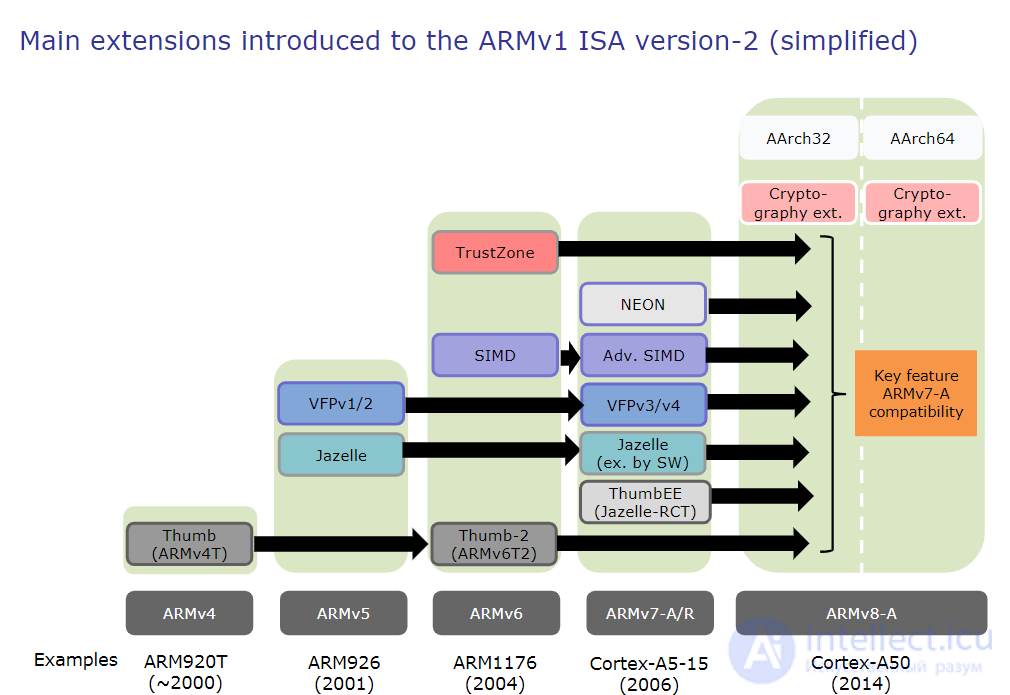

Архитектура ARM содержит следующие особенности RISC:

Одним из существенных отличий архитектуры ARM от других архитектур процессоров является так называемая предикация - возможность условного исполнения команд. Под "условным исполнением" здесь понимается то, что команда будет выполнена или проигнорирована в зависимости от текущего состояния флагов состояния процессора.

В то время как для других архитектур таким свойством, как правило, обладают только команды условных переходов, в архитектуру ARM была заложена возможность условного исполнения практически любой команды. Это было достигнуто добавлением в коды их инструкций особого 4-битового поля (предиката). Одно из его значений зарезервировано для того, чтобы инструкция могла быть выполнена безусловно, а остальные кодируют то или иное сочетание условий (флагов). С одной стороны, с учетом ограниченности общей длины инструкции, это сократило число бит, доступных для кодирования смещения в командах обращения к памяти, но с другой - позволило избавляться от инструкций ветвления при генерации кода для небольших if-блоков.

ARM процессор также имеет некоторые особенности, редко встречающиеся в других архитектурах RISC — такие, как адресация относительно счетчика программ (на самом деле счетчик команд ARM является одним из 16 регистров), а также пре- и пост-инкрементные режимы адресации.

ARM7 и более ранние версии имеют трехступенчатый конвейер. Это ступени переноса, декодирования и исполнения. Более производительные архитектуры, типа ARM9, имеют более сложные конвейеры. Cortex-a8 имеет 13-ступенчатый конвейер.

Архитектура предоставляет способ расширения набора команд, используя сопроцессоры, которые могут быть адресованы, используя команды регистрового обмена с сопроцессором MCR, MRC, MRRC, MCRR и похожие команды. Пространство сопроцессора логически разбито на 16 сопроцессоров с номерами от 0 до 15, причем 15й зарезервирован для некоторых типичных функций управления, типа управления кэш-памятью и MMUоперации (memory management unit — блок управления памятью).

В машинах на основе ARM периферийные устройства обычно подсоединяются к процессору путем сопоставления их физических регистров в памяти ARM или в памяти сопроцессора, или путем присоединения к шинам, которые в свою очередь подсоединяются к процессору. Доступ к сопроцессорам имеет большее время ожидания, поэтому некоторые периферийные устройства проектируются для доступа в обоих направлениях. В остальных случаях разработчики чипов лишь пользуются механизмом интеграции сопроцессора. Например, движок обработки изображений должен состоять из малого ядра ARM7TDMI, совмещенного с сопроцессором, который поддерживает примитивные операции по обработке элементарных кодировок HDTV (High-Definition Television- Телевидение высокой четкости).

ARM предоставляет 31 регистр общего назначения разрядностью 32 бит. В зависимости от режима и состояния процессора пользователь имеет доступ только к строго определенному набору регистров. В ARM state разработчику постоянно доступны 17 регистров:

Во всех режимах, кроме User mode и System mode, доступен также Saved Program Status Register (SPSR). Об этом говорит сайт https://intellect.icu . После возникновения исключения регистр CPSR сохраняется в SPSR. Тем самым фиксируется состояние процессора (режим, состояние; флаги арифметических, логических операций, разрешения прерываний) на момент непосредственно перед прерыванием

В большинстве существующих моделей микропроцессоров реализована шина PCI и возможность работы с внешней динамической оперативной памятью (DRAM). В процессорах, предназначенных для потребительских устройств, также обычно интегрируются: контроллеры шин USB, IIC, AC’97-совместимое звуковое устройство, устройство для работы с флэш-носителями стандарта SD и MMC, контроллер последовательного порта.

Все процессоры имеют линии ввода-вывода общего назначения (GPIO). В потребительских устройствах к ним могут быть подключены кнопки «быстрого запуска», сигнальные светодиоды, колесо прокрутки (JogDial), клавиатура.

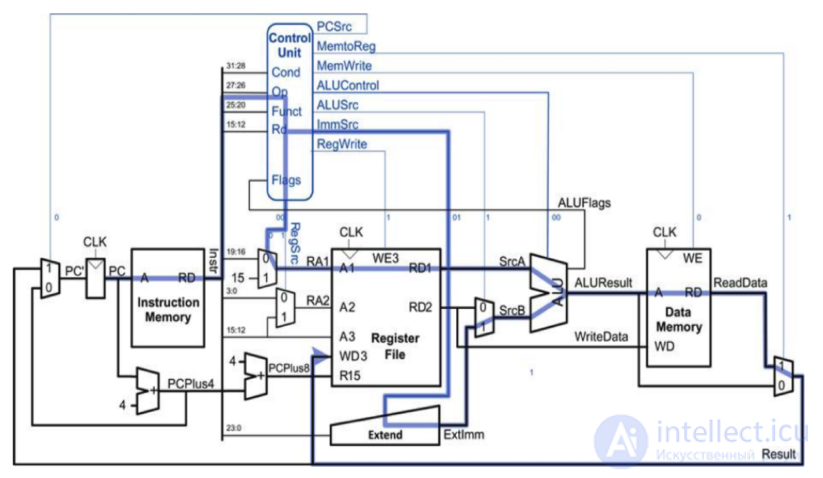

32-битная архитектура загрузки / сохранения с организацией в гарвардском стиле с использованием платы Altera DE1 FPGA. Ключевые компоненты процессора:

Были реализованы следующие инструкции:

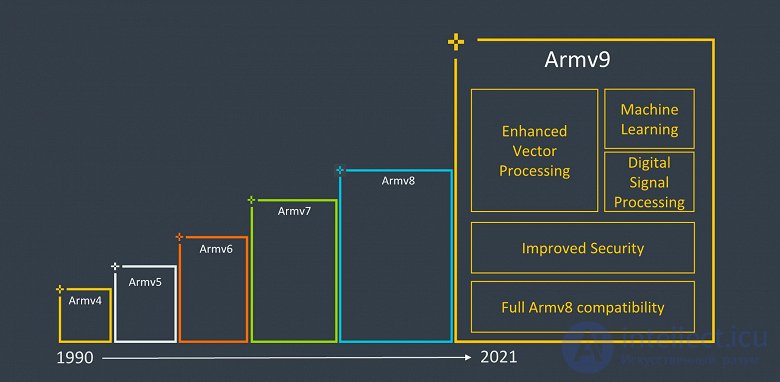

2006-2010 ARMv7 была создана компанией ARM Limited. А другие компании, например NVIDIA, LG, Samsung — покупают лицензию у ARM Limited на выпуск процессоров с такой архитектурой.

То есть ARMv7 — это не модель процессора, это именно его архитектура.Все процессоры ARMv7 поддерживают набор инструкций Thumb-2, благодаря которым современные приложения могут работать быстрее.

ARMv7 имеет обратную совместимость с ARMv4, ARMv5te и ARMv6.

Архитектура ARM претерпела несколько серьезных изменений и теперь поддерживает реализации в широком спектре точек производительности, с более чем миллиардом деталей в год, произведено. В версии (ARMv7) разнообразие формально признано в архитектуре.

Профили, используемые для адаптации архитектуры к различным требованиям рынка. Ключевым фактором является то, что уровень приложения согласован для всех профилей, и большая часть вариаций приходится на системный уровень.

Внедрение технологии Thumb-2 в ARMv6T2 обеспечило баланс между ARM и Thumb.

наборы инструкций и возможность расширения архитектуры ARM на новые рынки, в частности рынок микроконтроллеров. Чтобы максимально использовать эту возможность, профиль только для большого пальца

с новой моделью программиста (рассмотрение на системном уровне) был введен как уникальный профиль, дополняя сильные стороны ARM на рынках высокопроизводительных встраиваемых систем и систем реального времени.

Ключевые критерии для реализации ARMv7-M следующие:

• Возможность внедрения с лучшими в отрасли ограничениями по мощности, производительности и площади

- Возможности для простых конструкций трубопроводов, предлагающие передовые уровни производительности системы в широкий спектр рынков и приложений

• Высоко детерминированная работа

- Одноцикловое / низкоцикловое исполнение

- Минимальная задержка прерывания (короткие конвейеры)

- Бескэш-работа

• Превосходная цель C / C ++ - соответствует стандартам программирования ARM в этой области.

- Обработчики исключений - это стандартные функции C / C ++, введенные с использованием стандартных соглашений о вызовах.

• Разработан для глубоко встраиваемых систем.

- Устройства с низким креплением

- Включить новые возможности начального уровня для архитектуры ARM

• Поддержка отладки и профилирования программного обеспечения для систем, управляемых событиями.

ARMv7 реализует некоторые новые расширения или реализует новые версии для различных расширений.

Наиболее важные из них:

VFP

Vector Floating Point- сопроцессор для векторной (и скалярной) обработки операций с плавающей запятой. Хотя это необязательно, но почти всегда реализовано. Для ARMv6 и ARMv7 это де-факто стандартный сопроцессор с плавающей запятой, который позволяет аппаратно складывать, вычитать, делить и умножать как с одинарной, так и с двойной точностью. Это также позволяет ЦП выполнять пакет арифметических вычислений (один тип арифметических операций с пакетом операндов) с помощью одной инструкции. Однако вычисления выполняются последовательно, один за другим. Таким образом, это не поведение параллелизма на уровне данных, как можно было бы ожидать от истинной инструкции SIMD (например, MMX / SSE). Вместо того, чтобы рассчитывать ускорение, использование VFP приводит к экономии машинного кода, что в результате приводит также к ускорению всего процесса.

Технология Thumb

Набор инструкций ARM содержит только 32-битные инструкции. Однако не каждой инструкции действительно нужно так много места. Это может привести к неэффективности при загрузке инструкций из памяти и, конечно, излишне громоздкому машинному коду. Технология Thumb предназначена для оптимизации размера машинного кода путем замены некоторых из наиболее часто используемых 32-битных инструкций их 16-битными альтернативами.

NEON

Расширение NEON - это движок SIMD, предназначенный для пакетной обработки арифметических операций.

Как и в случае с VFP, операнды втягиваются как вектор в одной инструкции, что приводит к значительному ускорению обработки. Однако, в отличие от VFP, NEON обрабатывает весь пакет параллельно, тем самым не экономя только размер кода, но и значительно ускоряя само вычисление. NEON очень удобен, особенно при кодировании / декодировании мультимедиа, 2D / 3D графики и т. Д. Однако следует отметить, что NEON может работать со значениями с плавающей запятой только с одинарной точностью.

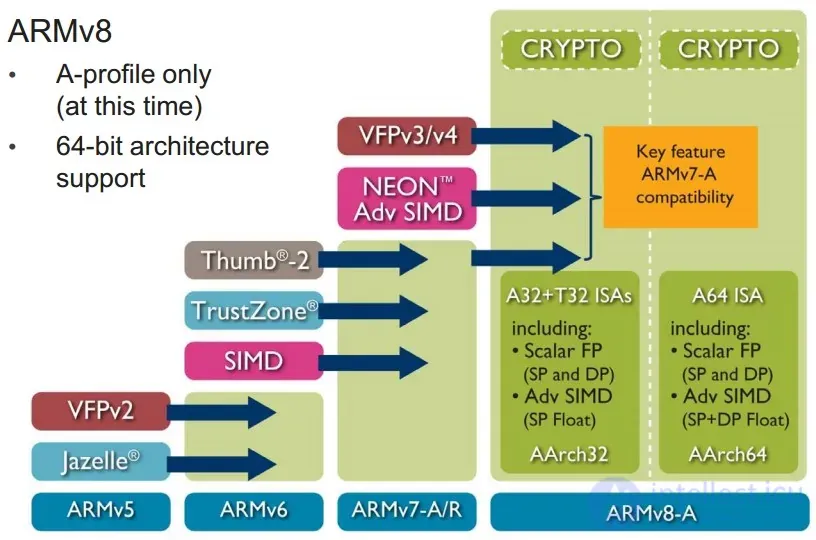

Обновленную архитектуру процессоров семейства ARMv8 окрестили именем AArch64. Она получила 64-битный набор инструкций и возможность работать с большим объемом оперативной памяти (4 Гбайт и больше). Само собой, предусмотрена совместимость с 32-битными приложениями (AArch32). Другими важными нововведениями ARMv8 стали:

— 31 регистр общего назначения, каждый длиной 64 бита, тогда как SP и PC не являются регистрами общего назначения. Чем выше разрядность регистров, тем больше числа можно в них хранить. А чем больше количество регистров, тем больше данних в них помещается одновременно. Как результат, за одну инструкцию можно обработать больший объем данних и весь алгоритм выполнится быстрее;

— трансляция виртуальных адресов из 48-битного формата работает с помощью механизмов LPAE, позаимствованных у ARMv7;

— новый набор инструкций с фиксированной длинной. Инструкции имеют размер 32 бита и многие совпадают с командами AArch32, хотя условных инструкций стало меньше;

— увеличено с 16 до 32 количество 128-битных регистров (совместимы с 64-битными регистрами), доступных сопроцессорам SIMD NEON и VFP, а также добавлены новые криптографические инструкции AES и SHA. Набор инструкций SIMD NEON ускоряет работу приложений, отвечающих за обработку медиаданных и сигналов. В свою очередь VFP отвечает за малоэнергозатратные вычисления над числами с плавающей запятой;

— поддержка вычислений над числами с плавающей запятой двойной точности и стандарта IEEE 754, который является общепринятым форматом представления чисел с плавающей запятой, используемый в программных реализациях арифметических действий.

2021 ARMv9 — больше похожа на договоренность между разработчиками компиляторов и архитекторами аппаратного обеспечения. Это своего рода соглашение о том, как в итоге должен выглядеть каждый конкретный процессор ARM. Какие инструкции нужно поддерживать и как они будут работать. Но в соглашении ничего не говорится о том, как это достигается с точки зрения транзисторов.

ARMv9 — это архитектура центрального процессора, что-то более абстрактное. Это похоже на соглашение между аппаратным и программным обеспечением. Архитектура обозначает, какие регистры должны быть на микропроцессоре и сколько бит они должны содержать, какие инструкции необходимо поддерживать и куда записывать результат после выполнения инструкции.

ARM9 . Чипы ARM9 могут достигать тактовой частоты 400 МГц. Эти чипы морально устарели, но по прежнему пользуются спросом. Например, в беспроводных маршрутизаторах и терминалах оплаты. Набор простых команд такого чипа позволяет с легкостью запускать многие Java-приложения.

ARM11 . Процессоры ARM11 могут похвастаться более полным набором простых команд, расширяющих их функционал и высокой тактовой частотой (вплоть до 1 ГГц). Благодаря невысокому энергопотреблению и низкой себестоимости чипы ARM11 до сих пор применяются в смартфонах начального уровня.

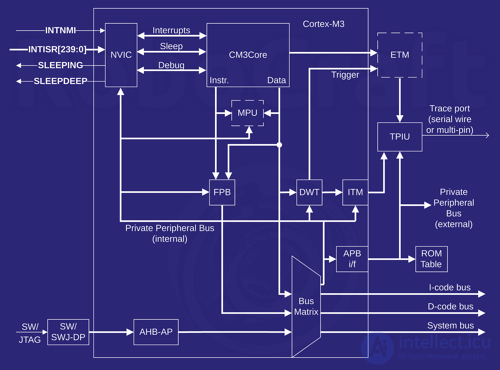

ARM Cortex-M3 в целом и конкретно STM32, потому что это важно для понимания многих особенностей работы этих микроконтроллеров в будущем — например, тактирование и принцип работы DMA. Прежде, чем приниматься за более сложные темы, мы изучим внутренности МК и их взаимодействие друг с другом.

Взглянем на схему Cortex-M3:

На ней обозначены «блоки», из которых состоит микроконтроллер, но на самом деле они взаимосвязаны и неотделимы друг от друга в реальной микросхеме. Более того, архитектура МК состоит из несколько уровней абстракции, а мы, не будучу профессиональными проектировщиками процессоров, будем рассматривать самый верхний и наименее детализированный во избежание опухания мозга. На этом уровне для нас наиболее важны три ключевых компонента.

Выполняет инструкции, производит вычисления в своем АЛУ (арифметико-логическом устройстве). Его Гарвардская архитектура позволяет одновременно загружать инструкции и осуществлять доступ к памяти — благодаря этому, а также трехступенчатому конвейеру, большинство инструкций выполняются за 1 такт. Ядро Cortex-M3 поддерживает набор инструкций Thumb-2, который содержит как 32-битные, так и 16-битные инструкции для сокращения объема кода за счет менее дальнобойных переходов; имеет 13 регистров общего назначения, снижая потребность в частом доступе к памяти.

Эта часть отвечает за генерацию прерываний на различные события: внешние — изменение логического уровня на входе ножки, пробуждение из режима сна; и внутренние — завершение приема/отправки данных, переполнение счетчика таймера и т.п. Контроллер поддерживает до 240 прерываний и до 256 уровней приоритета, причем вход в обработчик прерывания занимает 12 тактов (сохранение стекового фрейма и регистров) и прерывания могут быть вложенными: если во время обработки прерывания возникает прерывание с меньшим приоритетом, то второе будет обработано через 6 тактов после обработки первого. Кроме того, существуют немаскируемые прерывания — NMI (Non-Masked Interrupts), которые невозможно сбросить, не обработав, и которые прерывают выполнение программы независимо от каких-либо условий. Такие прерывания генерируются при сбое внешнего источника тактирования (кварца, керамического резонатора) и при обнаружении некорректной инструкции.

Современные процессоры содержат множество различных шин, к которым подключаются остальные устройства системы. На заре компьютерной эпохи шиной (bus) называли просто пачку проводников, соединяющих несколько устройств с процессором, который мог одновременно работать лишь с одним устройством, а остальные в это время простаивали, так как шина была на всех одна. К тому же, все устройства были вынуждены работать на одной скорости (самого медленного устройства), что удерживало рост производительности систем.

продолжение следует...

Часть 1 Тема 17. RISK и ARM– процессоры

Часть 2 Аппаратная модель STM32 - Тема 17. RISK и ARM– процессоры

Надеюсь, эта статья про risk, была вам полезна, счастья и удачи в ваших начинаниях! Надеюсь, что теперь ты понял что такое risk, arm и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Компьютерная схемотехника и архитектура компьютеров

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров