Лекция

Привет, сегодня поговорим про схемотехника цифровых элементов, обещаю рассказать все что знаю. Для того чтобы лучше понимать что такое схемотехника цифровых элементов, последовательностные цифровые схемы, триггеры, регистры , распределители тактов , настоятельно рекомендую прочитать все из категории Компьютерная схемотехника и архитектура компьютеров.

Цифровые устройства – это электронные устройства, предназначенные для обработки цифровых сигналов. Для описания работы цифровых устройств используется алгебра логики (Булева алгебра). При этом абстрагируются от физических значений уровня сигнала в вольтах, а рассматривают так называемые логические уровни: 0 – низкий и 1 – высокий.

Классификация цифровых устройств показана на рис.1.1.

Рисунок 1.1 – Классификация цифровых устройств

Последовательное во времени преобразование двоичной информации требует организации хранения исходных данных, промежуточных и конечных результатов на запоминающих элементах. Временное хранение данных необходимо для ожидания разновременно поступающих аргументов, для многократной передачи данных в разные устройства и т.д.

Большинство современных цифровых устройств являются последовательностными или цифровыми автоматами с памятью, состоящими из комбинационной схемы и элементов памяти – запоминающих элементов (ЗЭ) (рис.4.1).

Рис. 4.1. Обобщенная структура схемы с памятью

У элементов для запоминания двоичной информации должно быть три режима работы: запись, хранение и выдача информации.

В режиме хранения ЗЭ находятся в одном из двух состояний: нулевом или единичном.В режиме записи возможна запись «0» или «1». Режим выдачи обычно не организован. Как правило, ЗЭ имеют два постоянно действующих выхода: прямой ( - выход), отображающий состояние ЗЭ, и инверсный (

- выход), отображающий состояние ЗЭ, и инверсный ( -выход), равный инверсии сигнала на прямом выходе.

-выход), равный инверсии сигнала на прямом выходе.

Наличие памяти в схеме позволяет запоминать промежуточные состояния обработки и учитывать их значения в дальнейших преобразованиях. Выходные сигналы Y=(Y1, Y2, …, Ym) в схемах данного типа формируются не только по совокупности входных сигналов X=(Х1, Х2, …, Xn),но исостояний схем памяти. При этом различают текущий дискретный момент времени t и последующий (t+1) момент времени

(рис. 4.1).

Передача значения Q между моментами времени t и (t+1) осуществляется с помощью синхронизирующих импульсов (СИ).

К числу простейших цифровых элементов относятся триггера, регистры , счетчики и распределители уровней.

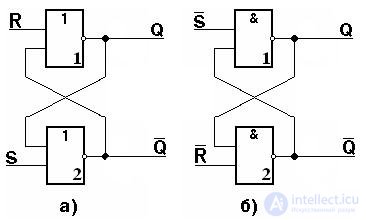

триггеры – элементарные автоматы, содержащие собственно элемент памяти (ЭП) или фиксатор и схему управления. Фиксатор строится на двух инверторах, связанных друг с другом «накрест», т.е. так что выход одного соединен с входом другого (рис. 4.2).

Рис. 4.2. Бистабильные ячейки на ЛЭ ИЛИ-НЕ (а) и И-НЕ (б)

Такое соединение дает цепь с двумя устойчивыми состояниями (поэтому ЭП называют еще бистабильной ячейкой (БЯ), т.е. с двумя стабильными состояниями). Действительно, если на выходе инвертора 1имеется логический ноль, то он обеспечивает на выходе инвертора 2 логическую единицу, благодаря которой сам и существует. То же согласование сигналов имеет место и для второго состояния, когда инвертор 1 находится в «1», а инвертор 2 – в «0». Любое из двух состояний может существовать неограниченно долго при условии наличия напряжения питания и отсутствия внешних сигналов управления.

Состояние триггера распознается по его выходному сигналу. Под влиянием входного сигнала триггер может скачкообразно переходить из одного устойчивого состояния в другое, при этом скачкообразно изменяется уровень напряжения его выходного сигнала. Переход в каждое последующее состояние обычно зависит не только от текущих значений входных сигналов, но и от предыдущего состояния триггера. Информация о предыдущем состоянии, поступающая с выходов вместе с внешними сигналами, управляет его работой. Поэтому триггеры являются устройствами с обратными логическими связями.

Триггеры в схемах вычислительных устройств обычно имеют два выхода: прямой  и инверсный

и инверсный  . В единичном состоянии на выходе

. В единичном состоянии на выходе  высокий уровень сигнала, а в пулевом – низкий. На выходе

высокий уровень сигнала, а в пулевом – низкий. На выходе  - наоборот.

- наоборот.

Схемы триггеров можно разделить на несколько типов: с установочными входами - RS – триггер, со счетными входом – Т-триггер, а также D-, JK- триггеры и др.

Если хотя бы по одному входу информация заносится принудительно под воздействием синхронизирующего сигнала, то триггер называется синхронизируемым (синхронным). Если занесение информации по любому входу производится без синхронизирующего сигнала, то триггер называется несинхронизируемым (асинхронным).

Законы функционирования триггеров задаются таблицами переходов.

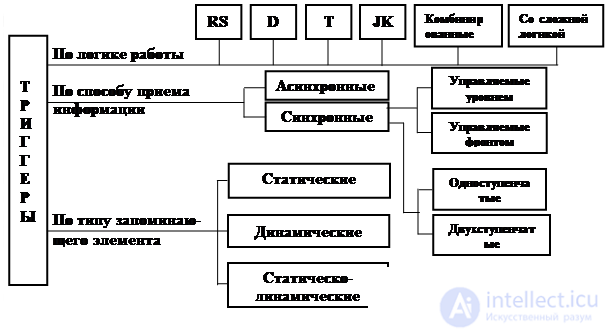

Классифицировать триггеры можно по разным признакам. На рисунке 4.3 дана классификация триггеров по трем важнейшим признакам: логике работы, способу записи информации и типу запоминающего элемента.

Рис. 4.3. Классификация триггеров, используемых в цифровой схемотехнике

Как уже упоминалось ранее, асинхронный триггер – это устройство, занесение информации по любому входу которого производится без синхронизирующего сигнала. Это значит, что состояние выходов таких триггеров зависит только от комбинации входных (информационных) сигналов и их текущего состояния.

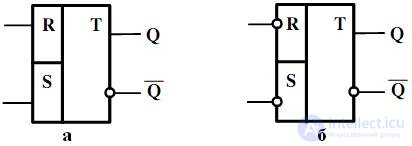

В зависимости от типа логических элементов, на основе которых построены бистабильные ячейки (БЯ) триггеров, различают триггера с прямой и инверсной входной логикой. На рис. 4.4,а представлено графическое обозначение RS триггера с прямой входной логикой, БЯ которого построена на элементах ИЛИ-НЕ (см. рис. 4.2,а). На рис. 4.4,б и 4.2,б представлены, соответственно, графическое обозначение RSтриггера с инверсными входами и БЯ на элементах И-НЕ, на базе которой он построен.

Работа этого триггера описана в табл. 4.1.

Таблица 4.1

| R | S | Qt | Qt+1 | Этапы на временной диаграмме | Примечание | |

| 0,6 | R=0; S=0 | Хранение информации | ||||

| 2,4 | ||||||

| Set | Установка в 1 | |||||

| Reset | Установка в 0 | |||||

| Х | R=1; S=1 | Запрещенная комбинация | ||||

| Х |

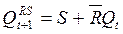

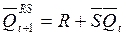

Функции выходов RS триггера ( характеристические уравнения):

(4.1)

(4.1)

. (4.2)

. (4.2)

Возможны различные виды функционирования RS триггера, познакомимся с ними:

Условное графическое обозначение этого триггера представлено на рис. 9.4, а временные диаграммы его работы – на рис. 9.5.

Рис. 4.4. Условное графическое обозначение асинхронного RS триггера с прямыми (а) и инверсными входами (б)

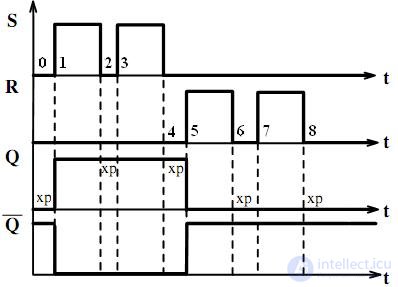

Рис. 4.5. Временные диаграммы работы асинхронного RS триггера с прямыми входами

На временных диаграммах представлены различные этапы состояния во времени входных и выходных сигналов асинхронного RS триггера в соответствии с таблицей 4.1, при этом, начальное состояние триггера в момент времен t=0 соответствует «0».

Существуют модификации RS триггеров по признаку их реакции на запрещенную (R=1 и S=1) комбинацию управляющих сигналов. В соответствии с этим признаком такие триггеры могут быть:

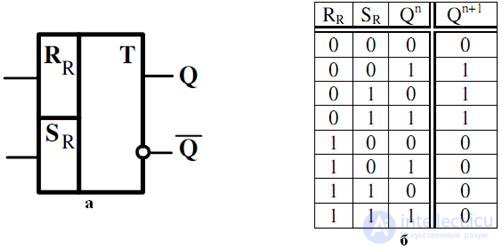

R-триггеры, отличающийся от RS триггера тем, что при наличии запрещенной комбинации на входе он устанавливается в «0». Условное обозначение этого триггера и таблица его работы представлены, соответственно, на рис. 4.6,а и 4.6,б.

S-триггер, отличающийся от RS триггера тем, что при наличии запрещенной комбинации на входе он устанавливается в «1». Условное обозначение этого триггера и таблица его работы представлены, соответственно, на рис. 4.7,а и 4.7,б.

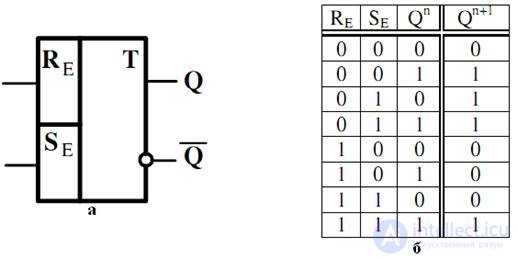

Е-триггер, отличающийся от RS триггера тем, что при наличии запрещенной комбинации на входе этот триггер сохраняет свое предыдущее состояние. Условное обозначение этого триггера и таблица его работы представлены, соответственно, на рис. 4.8,а и 4.8,б

Рис. 4.6. Графическое обозначение R-триггера (а) и таблица его работы (б)

Рис. 4.7. Графическое обозначение S-триггера (а) и таблица его работы (б)

Рис. 4.8. Графическое обозначение E-триггера (а) и таблица его работы (б)

DV-триггер

D-триггер

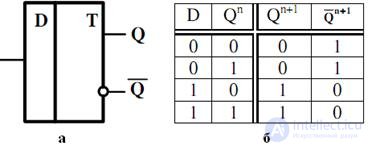

Триггер типа D (от английского Delay –задержка) имеет один вход. Его состояние на прямом выходе повторяет входной сигнал, но с задержкой, определяемой тактовым сигналом, поступающим на синхровход. Исходя из этого следует, что асинхронный D-триггер не имеет практического применения. Тем не менее, в целях дальнейшего освоения теории триггерных устройств представляем графическое обозначение D-триггера (рис. 4.9,а) и таблицу его работы (рис. 4.9,б).

Рис. 4.9. Графическое обозначение D-триггера (а) и таблица его работы (б)

Характеристическое уравнение прямого и инверсного выходов D-триггера, составленные на основании таблицы переходов, имеют вид:

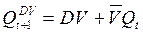

(4.3)

(4.3)

. (4.4)

. (4.4)

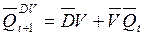

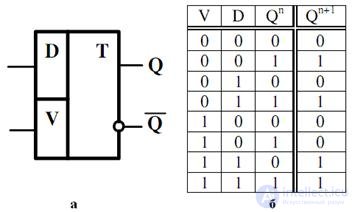

DV-триггер отличается от D-триггера тем, что благодаря управляющему сигналу Vпредставляется возможность избежать недостатка, присущего асинхронному D-триггеру. А именно: если вход V=0, то DV-триггер хранит информацию (см. таблицу рис. 4.10,б), а при V=1 – он работает как D-триггер. На рис. 4.10,а представлено графическое обозначение DV-триггера, а выражения (4.5) и (4.6) описывают функции прямого и инверсного выходов этого триггера.

(4.5)

(4.5)

. (4.6)

. (4.6)

Рис. 4.10. Графическое обозначение DV-триггера (а), таблица его работы (б)

Прежде, чем познакомиться с данным триггером, необходимо отметить принципиальное отличие триггера этого типа, а также триггера JK типа (будет рассмотрен позже), от раннее рассмотренных типов триггеров. Различие заключается в том, что RS- и D-триггера имеют разомкнутую структуру (о внутренних обратных связях в схеме БЯ сейчас речь не идет), а триггера T- и JKтипа используют выходные сигналы для воздействия на свои входы.

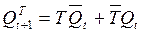

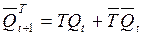

T-триггер – устройство, меняющее свое состояние на противоположное при поступлении активного уровня сигнала на его вход. Т.е. при поступлении на вход этого триггера серии сигналов, состоящей из «0» и «1», на выходе по приходу каждой второй «1», на прямом выходе триггера будет «0», при условии нулевого начального его состояния. Получается, что Т-триггер считает «1» на своем входе и, если на вход поступило четное количество «1» (или «0» при инверсном входе), на его выходе будет «0», в противном случае – «1». Из-за этого Т вход этого триггера называют счетным. Таблица работы этого триггера представлена на рис. 4.11,б, графическое обозначение – на рис. 4.11,а. Характеристическое уравнения его прямого и инверсного выходов имеют, соответственно, вид (4.7) и (4.8).

(4.7)

(4.7)

. (4.8)

. (4.8)

Рис. 4.11. Графическое обозначение Т-триггера (а), таблица его работы (б)

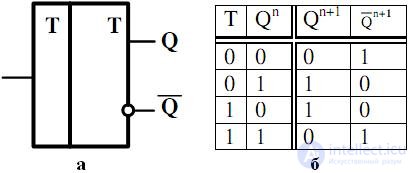

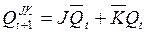

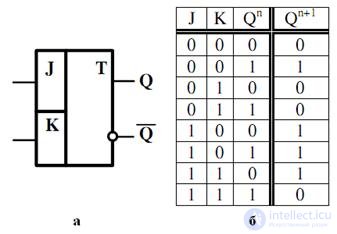

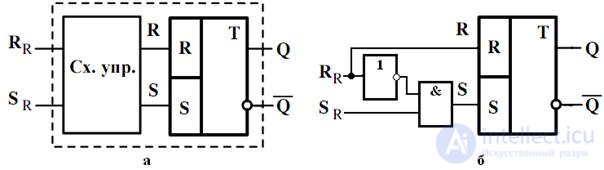

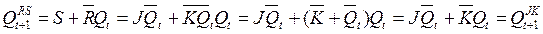

JK-триггер отличается от RS-триггера тем, что при наличии на его входе запрещенной комбинации состояния выходов JK-триггераинвертируются. Для этого так же, как и Т-триггер JK-триггер использует свои выходы для воздействия на свои входы.

Графическое обозначение этого триггера представлена на рис. 4.12,а, таблица работы – на рис. 4.12,б . Характеристическое уравнения его прямого и инверсного выходов имеют, соответственно, вид (4.9) и (4.10).

(4.9)

(4.9)

. (4.10)

. (4.10)

Рис. 4.12. Графическое обозначение JK-триггера (а), таблица его работы (б)

В отличие от не тактируемых триггеров, переход в новое состояние в синхронных (тактируемых) триггерах, имеющих специальный вход, происходит только при подаче на этот вход тактовых сигналов. Тактовые сигналы называют также синхронизирующими,исполнительными, командными и т.д. и обозначаются буквой C (от слова Clock – часы, в данном случае подразумевается «управление по времени»).

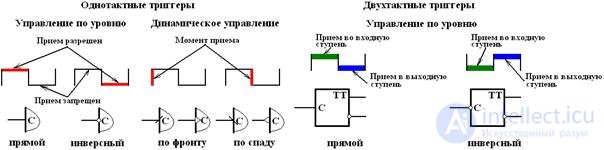

По способу восприятия тактовых сигналов триггеры делятся на управляемые уровнем иуправляемые фронтом.

Управление уровнем означает, что при одном уровне тактового сигнала триггер воспринимает входные сигналы и реагирует на них, а при другом не воспринимает и остается в неизменном состоянии.

При управлении фронтом разрешение на переключение дается только в момент перепада тактового сигнала (на его фронте или спаде) В остальное время независимо от уровня тактового сигнала триггер не воспринимает входные сигналы и остается в неизменном состоянии. Триггеры, управляемые фронтом, называют также триггерами сдинамическим управлением.

Помимо деления синхронных триггеров по способу восприятия тактовых сигналов триггеры делятся еще и по характеру процесса переключения: на одноступенчатые идвухступенчатые. В одноступенчатом триггере переключение в новое состояние происходит сразу, в двухступенчатом – по этапам.

На рис. 4.13 показаны процессы, происходящие в синхронных триггерах. На диаграммах тактовых импульсов отмечено содержание процессов на отдельных этапах переключения триггеров, под диаграммами даны обозначения синхронизирующего входа для различных видов синхронизации.

Рис. 4.13 Процессы, происходящие в синхронных триггерах

В качестве примера функционирования синхронных триггеров рассмотрим работу синхронного RS-триггера. Работа этого триггера описывается таблицей 4.2.

Таблица 4.2

| С | R | S | Qt | Qt+1 | С | R | S | Qt | Qt+1 |

| X | |||||||||

| X |

Сравнивая таблицы 4.1 и 4.2 работы, соответственно, асинхронного и синхронного RS-триггера, видно, что вторая отличается от первой тем, что в ней появился входной сигнал синхронизации С.

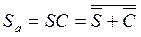

Как мы видим, первые восемь комбинаций входных сигналов синхронного триггера соответствуют значению С=0, при котором ни одна комбинация сигналов RиS не приводит к изменению его состояния. Об этом говорит сайт https://intellect.icu . При С=1 работа синхронного RS-триггераповторяет работу асинхронного. Из этого следует, что если в характеристическом уравнении аргументы Ra и Sa заменить, соответственно, на функции Ra =RС и Sa = SС, где Ra и Sa – входные сигналы асинхронного и R, S и С –входные сигналы синхронногоRS-триггера, то характеристическое уравнение для асинхронного и синхронного триггеров будут одно и то же.

Если БЯ, заложенная в основу асинхронного RS-триггера, построена на ЛЭ ИЛИ-НЕ, то функции Ra и Sa для синхронного триггера в этом же базисе примут вид:  и

и  .

.

Вид этих же функции, но в базисе И-НЕ, с учетом инверсных входных сигналов БЯ (см. рис. 4.2,б) следующий:  и

и  .

.

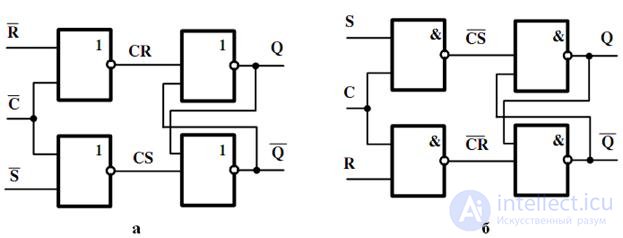

На рис. 4.14 представлены функциональные схемы синхронного RS-триггера в базисе ИЛИ-НЕ (а) и И-НЕ (б).

Рис. 4.14. Функциональная схема синхронного RS-триггера в базисе ИЛИ-НЕ (а) и И-НЕ (б)

Синхронный RS триггер с синхронизацией по фронту

RS триггер с синхронизацией по уровню

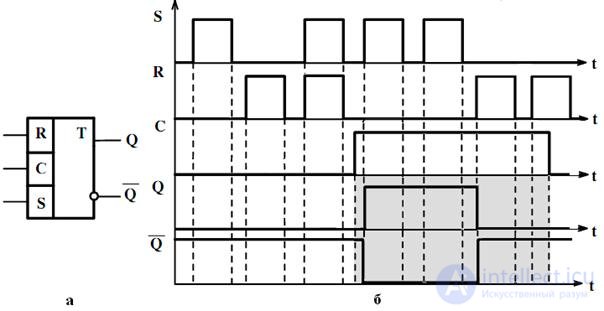

На рис. 4.15, представлено графическое обозначение RS-триггера с синхронизацией по уровню с прямыми входами. Для изменения информации в таком триггере д.б. активным («1»), помимо сигнала на одном из информационных входов, еще и сигнал на синхронизирующем входе (см. рис. 4.15,б).

Как видно из представленных временных диаграмм работы этого триггера, момент егопереключения (перехода из одного состояния в другое) определяетсямоментом появления сигнала единичного уровня на одном из информационных входов, при условии наличия «1» на синхронизирующем входе, или моментом установления «1»насинхронизирующемвходе,при условии присутствия«1»наодном из информационныхвходов. Это справедливо для триггеров положительной логики с любой логикой работы с синхронизацией по уровню.

Рис. 4.15. Графическое обозначение синхронного триггера (а) и временные диаграммы его работы (б)

В отличие от синхронного триггера с синхронизацией по уровню, момент переключения триггера с синхронизацией по фронту определяется моментом переключения сигнала на синхровходе при условии наличия в этот момент активного уровня на одном из управляющих его входов. Если на момент действия активного для данного типа триггера фронта на управляющих его входах не будет присутствовать активный уровень сигнала, то триггер останется в режиме хранения.

Рис. 4.16. Графическое обозначение синхронного RS триггера с синхронизацией по переднему (а) и заднему (б) фронту и временные диаграммы их работы, соответственно, (в) и (г).

С учетом того, что существует два момента переключения синхросигнала: переход изсостояния «0» в состояние «1» и из состояния «1» в состояние «0», существует две разновидности таких триггеров. На рис. 4.16,а представлено графическое обозначение синхронного RS триггера с синхронизацией по переднему фронту (из «0» в «1») и временные диаграммы его работы в момент переключения (рис. 4.16, в). На рис. 4.16,б и 4.16,г представлены, соответственно, графическое обозначение синхронного RS триггера с синхронизацией по заднему фронту (из «1» в «0») и временные диаграммы его работы.

Рассмотренные триггерные устройства, относящиеся к классу одноступенчатых триггеров, содержат только одну БЯ. Как только на входе одноступенчатого триггера изменяется установочная комбинация, на выходах немедленно (без учета переходных процессов) изменяются выходные уровни, свидетельствующие об изменении состояния триггера. Подобная реакция в ряде случаев недопустима. В общем случае она не позволяет управлять выработкой новых значений установочных входов собственным действующим состоянием, а также состояниями всех других переключаемых в том же такте триггеров. В частности, одноступенчатые триггеры нельзя непосредственно использовать в сдвигающих регистрах, в одноразрядных пересчетных схемах по модулю 2 и т.д.

Во всех подобного рода схемах используются двухступенчатые триггеры, содержащие не менее двух БЯ. Такие триггеры называют MS – триггерами (Master–Slave – ведущий-ведомый). Оба триггера функционируют как синхронные триггеры со статическим управлением (рис. 4.17).

Рис. 4.17. Схема функциональная двухступенчатого триггера

Если на синхронизирующем входе С=1, ведущий триггер устанавливается в состояние, соответствующее сигналам, поступающим на информационные входы. Ведомый триггер, имеющий инверсный синхронизирующий вход, при этом невосприимчив к информации, поступающей на его вход с выхода ведущего триггера. Он продолжает находиться в состоянии, в которое был ранее установлен (в предыдущем тактовом периоде). При изменении значения С (с «1» на «0») ведущий триггер отключается от информационных входов и перестает реагировать на изменения сигналов на этих входах; ведомый триггер устанавливается в состояние, в котором находится ведущий триггер. С этого момента на выходах устанавливаются значения, соответствующие входным сигналам, поступавшим к моменту рассматриваемого фронта сигнала на синхронизирующем входе.

Таким образом, управление процессами в триггере с двухступенчатым запоминанием информации за время тактового периода осуществляется двумя фронтами сигнала на синхронизирующем входе: на положительном фронте происходит установка ведущего триггера, на отрицательном – ведомого.

МS-триггеры строятся на основе двухступенчатых синхронных RS-, JK-триггеров и других. Ниже рассматриваются двухступенчатые триггеры на основе перечисленных триггеров.

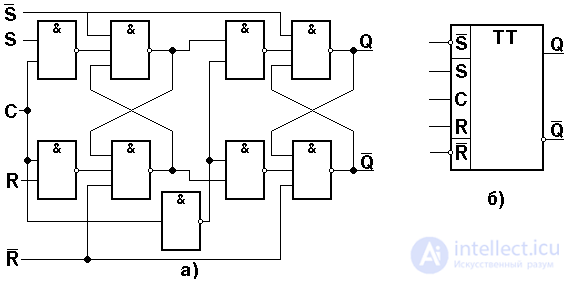

Синхронный двухтактный RS-триггер. Устойчивая работа однотактного RS-триггера в произвольной схеме возможна только при условии, что информация в триггер заносится после завершения передачи информации о прежнем его состоянии в другой триггер. Для этого приходится использовать две серии находящихся в противофазе синхроимпульсов. Этот принцип обмена информацией реализован в двухтактных RS-триггерах (рис. 4.18).

|

Рис. 4.18. Схема функциональная двухтактного RS-триггера на элементах И-HE (а) и его условное графическое обозначение (б)

При поступлении на вход импульса С=1 входная информация заносится только в первый однотактный RS-триггер, а второй триггер при этом будет хранить информацию, относящуюся к предыдущему периоду представления. По окончании действия импульса синхронизации ( =0,

=0,  =1) первый RS-триггер перейдет в режим хранения, а второй перепишет из него новое значение выходного сигнала. Двухтактный триггер изменит свое состояние только после окончания действия импульса синхронизации (переход в режим хранения информации). Для установки триггера в состояние 0 или 1 без использования синхроимпульсов в схему введены дополнительные входы

=1) первый RS-триггер перейдет в режим хранения, а второй перепишет из него новое значение выходного сигнала. Двухтактный триггер изменит свое состояние только после окончания действия импульса синхронизации (переход в режим хранения информации). Для установки триггера в состояние 0 или 1 без использования синхроимпульсов в схему введены дополнительные входы  и

и  не синхронизируемой установки.

не синхронизируемой установки.

В практической цифровой схемотехнике иногда встречаются ситуации, когда возникает необходимость проектирования триггеров с требуемой логикой работы на базе имеющихся в наличии триггеров.

Для решения этой проблемы существуют следующие методы проектирования триггеров:

- метод проектирования с использованием RS-триггера,

- метод преобразования характеристического уравнения,

- метод сравнения характеристических уравнений.

Проектирование триггеров на основе RS-триггера

Рассмотрим этот метод на примере проектирования модификаций RS-триггера: R-триггера. При проектировании триггеров на основе RS-триггера необходимо спроектировать схему управления его входами.

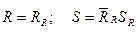

Для R триггера: RR и SR– входы схемы управления, R и S– выходы схемы управления и входы RS-триггера. По определению, R-триггер при наличии запрещенной комбинации должен установиться в «0», а для RS-триггера – это режим установки в «0» (R=1, S=0). Исходя из этого следует, что функции выходов разрабатываемой схемы управления RS-триггером (см. рис. 4.19,а) будут иметь вид (10.1)

. (4.11)

. (4.11)

Рис. 4.19. Исходная схема для проектирования R-триггера и функциональная схема R-триггера в произвольном базисе (б)

Суть данного метода поясним в процессе проектирования JK-триггера на основе RS-триггера.

Сравним выражения (4.1) и (4.9), описывающие функции прямых выходов, соответственно RS- и JK-триггеров, а также (4.2) и (4.10), описывающие функции инверсных выходов, соответственно RS- и JK-триггеров. В результате сравнения получим, что

и

и  . (4.12)

. (4.12)

Подставив в (4.1) и (4.2) вместо аргументов R и S, значения функций (4.12) и выполнив необходимые преобразования, получаем в результате:

(4.13)

(4.13)  (4.14)

(4.14)

Доказательства (4.13) и (4.14) подтверждают справедливость (4.12), а это значит являются функциями выходных сигналов схемы управления RS-триггера, позволяющими на его основе реализовать функции JK-триггера.

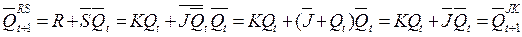

Функциональная схема спроектированного JK-триггера представлена на рис. 4.20.

Рис. 4.20. Функциональная схема JK-триггера на базе RS-триггера на логических элементах И

Функциональные схемы двух триггеров (R- и JK-), построенных на базе одного и того же RS-триггера, позволяют наглядно продемонстрировать понятия разомкнутой изамкнутой структуры триггеров, о которых упоминалось ранее. На рис. 4.19отсутствуют обратные связи с выходов RS-триггера на вход схемы управления этим триггером, что и является признаком того, что структура R-триггера являетсяразомкнутой. Из рис. 4.20 видно, что на схему управления RS-триггера – основы для проектирования JK-триггера поступают помимо входных сигналов J и K поступают сигналы  и

и  RS-триггера, что является признаком замкнутой структуры JK-триггера.

RS-триггера, что является признаком замкнутой структуры JK-триггера.

Т-триггер

Существуют универсальные триггеры, на базе которых можно проектировать другие триггера. К таким триггерам относятся JK- и DV-триггеры

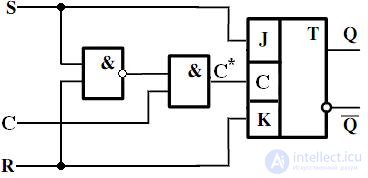

Для пояснения данного метода рассмотрим процесс проектирования RS-триггера на базе JK-триггера.

Сравнивая характеристические уравнения этих триггеров, можно сделать вывод о том, что на базе JK-триггера можно построить RS-триггер, если обеспечить условие JK=0. Реализовать это условие для асинхронных триггеров не представляется возможным, т.к. не представляется возможным описать функции выходов J иK схемы управления базового JK-триггера, определяемые ее аргументами R и S. Однако, если в качестве базового триггера взять синхронный JK-триггер, то с помощью функций: K=R, J=S и  , где K , J и С*– информационные входы и синхронизации базового JK-триггера, а R, S и С - информационные входы и синхронизации проектируемого RS–триггера, мы достигаем поставленной цели. Функциональная схема спроектированного по данному методу RS–триггера на базе JK-триггера представлена на рис. 4.21.

, где K , J и С*– информационные входы и синхронизации базового JK-триггера, а R, S и С - информационные входы и синхронизации проектируемого RS–триггера, мы достигаем поставленной цели. Функциональная схема спроектированного по данному методу RS–триггера на базе JK-триггера представлена на рис. 4.21.

Рис. 4.21. Функциональная схема RS–триггера на базе JK-триггера

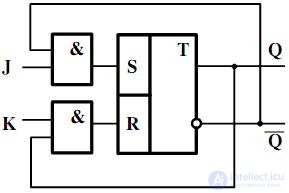

Схемы синхронных RS- и JK-триггеров составляют основу для получения других триггерных схем. На рис. 4.22÷4.24 представлены различные схемные решения триггеров, построенных на их основе.

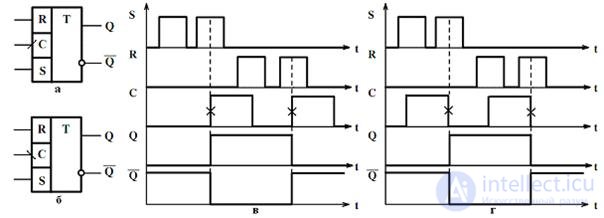

Рис. 4.22. Т-триггер: (а) – несинхронизируемый, (б) - его временная диаграмма, (в) – синхронизируемый и (г), (д) – соответственно, условное графическое обозначение и его временная диаграмма

Простейшая схема несинхронизируемого Т-триггера представлена на рис. 4.22,а. При Т=1 для двухступенчатого триггера сигнал на его выходе изменится только по завершению действия Т=1, что способствует возникновению генерации в схеме с обратной связью. Можно считать, что в данной схеме единичный входной сигнал представляется спадом сигнала Т=1, так как при любой продолжительности сигнала Т=1 изменение состояния Т-триггера происходит только 1 раз – при снятии сигнала Т=1 (рис. 4.22,б).

Для представления потенциалом последовательности единиц на входе Т-триггера используется синхронизируемая схема (рис. 4.22,в, г). Здесь единичный входной сигнал представляется высоким уровнем сигнала Т при С=1. Поэтому высоким уровнем сигнала Т можно представить последовательность 1 (рис. 4.22,д). Запись в триггер происходит при С=1, причем смена состояния происходит после окончания действия сигнала синхронизации С=1. При Т=1 состояние триггера изменяется на противоположное, а при Т=0 не меняется.

Наиболее широко используемый, реализует функцию временной задержки. Предназначен для хранения состояний (1 или 0) на один период тактовых импульсов (задержка на один такт). Имеет режимы установки 1 или 0. В связи с этим несинхронизируемый D-триггер (рис. 4.23,а) не применяется, т.к. на его выходе будет просто повторяться входной сигнал. Синхронизируемый однотактный D-триггер (рис. 4.23,б) задерживает распределение входного сигнала на время паузы между синхросигналами (задержка на полупериод). D (Delay – задержка) – вход установки в единичное или нулевое состояние на время, равное одному такту.

|

При С=1 триггер устанавливается в состояние, определяемое логическим уровнем на входе D (при С=0 он сохраняет ранее установленное состояние  ). Такое функционирование может быть описано логическим выражением:

). Такое функционирование может быть описано логическим выражением:  . D-триггер можно спроектировать на базе любых RS- или JK-триггеров, если на их входы одновременно подать взаимно инверсные сигналы.

. D-триггер можно спроектировать на базе любых RS- или JK-триггеров, если на их входы одновременно подать взаимно инверсные сигналы.

Рис. 4.23. D-триггер: (а) – несинхронизируемый; (б) – синхронизируемый однотактный; (в) – двухтактный и его условное графическое обозначение (г); (д) – временная диаграмма работы двухтактного D-триггера

На рис. 4.24 представлены варианты построения различных триггеров на базе синхронного JK-триггера.

Рис. 4.24. Способы использования JK-триггера

Регистр – последовательностное логическое устройство, осуществляющее прием и запоминание n- разрядного слова (кода), х1, х2,… хn-1, xn, а также выполнение определенных микроопераций над этим словом. Число разрядов в регистре называют его длиной. В n-разрядном регистре может быть записано 2n различных n-разрядных двоичных чисел, т.е. находится в 2n различных состояниях. Регистр представляет собой упорядоченную совокупность триггеров (RS-, D- или JK- типов с динамическим или статическим управлением). Разрядность регистра соответствует количеству используемых в нем триггеров. Каждый триггер имеет прямой и инверсный выходы, используемые соответственно для получения прямого и инверсного кодов. Кроме триггеров в состав регистра входит комбинационная схема, формирующая функцию возбуждения (входные сигналы) триггеров. Регистры – самые распространенные узлы цифровых устройств. Они оперируют с множеством связанных переменных, составляющих слово. Над словами выполняется ряд операций: прием, хранение, сдвиг в разрядной сетке. С помощью регистров можно осуществлять операции преобразования информации из одного вида в другой (последовательного кода слова в параллельный и т.п.), а также некоторые логические операции (поразрядное логическое сложение и умножение и т.п.).

По виду выполняемых операций над словами различают регистры накопительные(памяти, хранения), предназначенные для приема и передачи информации, исдвигающие.

По количеству входных каналов регистры бывают одно- и парофазными. В однофазных регистрах информация поступает на каждый разряд только по одному каналу (прямому или инверсному), а в парофазных – по обоим каналам.

По количеству тактов управления, необходимых для записи кода слова, различают одно-, двух- и многотактные(n-тактные) регистры.

По способу приема и передачи информации различают последовательные (с записью кода числа путем его последовательного сдвига тактирующими сигналами, начиная с младшего или старшего разряда), параллельные (с записью числа во все разряды одновременно параллельным кодом) и параллельно- последовательные регистры.

В параллельных регистрах прием и выдача слов производится по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям.

В последовательных регистрах слова принимаются и выдаются разряд за разрядом. Их называют сдвигающими, т.к. тактирующие сигналы при вводе и выводе слов перемещают их в разрядной сетке. Сдвигающий регистр может быть нереверсивным (с однонаправленным сдвигом) или реверсивным (с возможностью сдвига в обоих направлениях).

Последовательно-параллельные регистры имеют входы-выходы одновременно последовательного и параллельного типа. Существует несколько вариантов последовательно-параллельных регистров: с последовательным входом и параллельным выходом (SIPO, Serial Input – Parallel Output), параллельным входом и последовательным выходом (PISO, Parallel Input – Serial Output), а также варианты с возможностью любого сочетания способов приема и передачи слов.

Для современной схемотехники характерно построение регистров на триггерах, преимущественно с динамическим управлением. Многие регистры имеют выходы с третьим состоянием, некоторые из них относятся к числу буферных, т.е. рассчитаны на работу с большими емкостными и/или низкоомными активными нагрузками. Это обеспечивает их работу непосредственно на магистраль без дополнительных схем интерфейса.

Назначение регистров памяти – хранение двоичной информации небольшого объема в течение короткого промежутка времени. Регистры представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись) и вывод (считывание) информации производится параллельным кодом. Ввод обеспечивается тактовым импульсом (с приходом очередного тактового импульса записанная информация обновляется). Считывание производится в прямом или обратном коде.

На рис. 4.25 приведена схема двухтактного регистра на основе RS –триггеров. Информация в регистр заносится по шинам х1, х2, …хn , только в том случае, когда на шину Пр подан управляющий сигнал приема информации.

При этом через схему &1 проходят сигналы установки триггеров в состояние 1 только в тех разрядах, где х1=1. Чтобы в остальных разрядах был записан 0, необходимо предварительно все разряды устанавливать в нулевое состояние. Записанный в регистр код слова будет храниться в нем до тех пор, пока не будет снова подан сигнал установки в состояние 0. Прямой код хранимого в регистре слова, будет выдан при наличии на шине Вп управляющего сигнала «Выдача прямого кода». При этом код слова с прямых выходов триггеров регистра пройдет через группу схем &2 и в каждом разряде на выходе будет выработан сигнал  .

.

Сигнал «Выдача инверсного кода» Ви позволяет через группу схем &3 получить инверсное значение кода, хранимого в регистре. При этом в каждом его разряде вырабатывается значение кода  .

.

Рис. 4.25. Схема функциональная двухтактного регистра на RS- триггерах

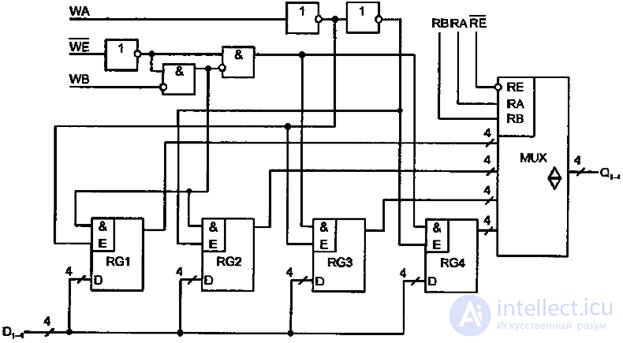

Из статических регистров (регистров памяти) составляются блоки регистровой памяти -регистровые файлы. Такие блоки позволяют осуществлять независимую и одновременную запись одного слова и чтение другого.

К примеру, микросхема ИР26 из серии КР1533 или К555 позволяет хранить 4 четырехразрядных слова. Информационные входы регистров RG1÷RG4 соединены параллельно (см. рис. 4.26). Входы адресов записи WA и WB дают 4 комбинации, каждая из которых позволяет соответствующему регистру принять информацию с входов данныхD1-4 при условии наличия на входе разрешения записи  активного низкого уровня сигнала. При высоком уровне сигнала на входе

активного низкого уровня сигнала. При высоком уровне сигнала на входе  входы данных и адресов запрещены. Выходные данные выдаются с данного регистрового файла в прямом коде.

входы данных и адресов запрещены. Выходные данные выдаются с данного регистрового файла в прямом коде.

Рис. 4.26. Схема регистрового файла

Содержимое файла (выход одного из регистров RG1÷RG4) вызывается на выход блокаQ1-4 с помощью дешифратора считывания (адресных входов мультиплексора) адресами RА и RВ при условии присутствия низкого активного уровня сигнала разрешения чтения  . При высоком уровне сигнала

. При высоком уровне сигнала  выходы блока Q1-4 находятся в состоянии высокого импеданса.

выходы блока Q1-4 находятся в состоянии высокого импеданса.

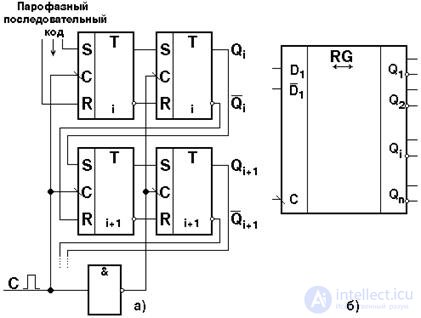

Предназначены для выполнения операции поразрядного сдвига хранимого двоичного слова информации после каждого тактового импульса (по сигналу С), т.е для перемещения всех цифр слова в направлении от старших к младшим разрядам (сдвиг вправо) или от младших к старшим разрядам (сдвиг влево). Реверсивный сдвигающий регистр способен сдвигать информацию как влево, так и вправо. Сдвиг кода влево на один разряд соответствует умножению кода числа на основание системы счисления, а сдвиг вправо - делению. Это объясняется тем, что вес каждого разряда кода для позиционной системы счисления определяется его позицией в коде. В регистре сдвиг числа на к разрядов осуществляется за к тактов или же за к микроопераций сдвига. Сдвигающий регистр содержит такие же схемы передачи по входам, как и регистры приема и передачи информации, но триггеры должны быть двойными типа MS (см. рис 4.27). Если использовать простые триггеры, например RS, то необходимо использовать еще один дополнительный регистр для промежуточного запоминания слова в процессе сдвига, т.е. каждый разряд регистра будет состоять из двух триггеров (рис. 4.28).

Рис. 4.27. Схема функциональная n-разрядного регистра на D – триггерах

Рис. 4.28. Схема функциональная двух разрядов сдвигающего регистра на RS – триггерах (а) и условное графическое обозначение регистра (б)

Сдвигающий регистр можно использовать не только для сдвига кода, но и для преобразования параллельного кода, принятого в регистр, в последовательный. Для этого достаточно принятый код сдвигать до тех пор, пока весь он не будет выдвинут из регистра. Данный регистр может выполнять функцию также преобразования последовательного кода в параллельный. С точки зрения уменьшения количества связей и оборудования регистры целесообразно строить на D – триггерах (рис. 4.27). Установка регистра в состояние «0» выполняется отрицательным импульсом, подаваемым на вход  . Параллельный код поступает на входы Х1÷Х4. Запись параллельного кода осуществляется положительным импульсом, подаваемым на вход С2. Последовательный код поступает на вход D1 и записывается в первую ступень триггера с выходом Q1 по положительному фронту синхросигнала С1. В первые ступени триггеров с выходами Q2-4по этому же фронту переписываются выходы вторых ступеней триггеров с выходами Q1-3. По заднему фронту сигнала С1 информация с первых ступеней триггеров Q1-4переписывается в их вторые ступени.

. Параллельный код поступает на входы Х1÷Х4. Запись параллельного кода осуществляется положительным импульсом, подаваемым на вход С2. Последовательный код поступает на вход D1 и записывается в первую ступень триггера с выходом Q1 по положительному фронту синхросигнала С1. В первые ступени триггеров с выходами Q2-4по этому же фронту переписываются выходы вторых ступеней триггеров с выходами Q1-3. По заднему фронту сигнала С1 информация с первых ступеней триггеров Q1-4переписывается в их вторые ступени.

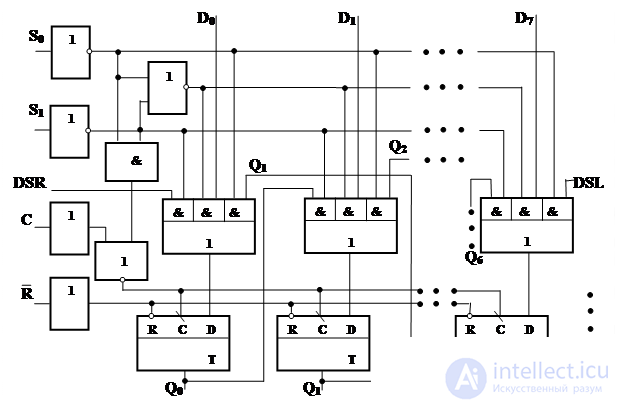

В сериях ИС и библиотеках БИС/СБИС программируемой логики имеется множество вариантов регистров (в схемотехнике ТТЛШ их около 30). Среди них есть многорежимные (многофункциональные) или универсальные, способные выполнять набор микроопераций. Многорежимность достигается композицией в одной и той же схеме частей, необходимых для выполнения различных операций. Управляющие сигналы, задающие вид выполняемой операции, активизируют необходимые для этого части схемы.

Типичным представителем многорежимных регистров является микросхема ИР13 серии КР1533 (см. рис. 4.29). Это восьмиразрядный регистр с возможностью двухсторонних сдвигов. Регистр имеет также параллельные входы и выходы (DSR – Data Serial Right, DSL - Data Serial Left), вход асинхронного сброса  и входы выбора режима S0 и S1, задающие четыре режима (параллельная загрузка, два сдвига и хранение).

и входы выбора режима S0 и S1, задающие четыре режима (параллельная загрузка, два сдвига и хранение).

Рис. 4.29. Схема функциональная многорежимного регистра

Функционирование регистра определяется таблицей 4.2. В таблице применяются следующие сокращения состояния входов и выходов:

Х – безразличное состояние, L – низкий уровень (лог. «0»),

Н – высокий уровень (лог. «1»), - положительный фронт.

Н – высокий уровень (лог. «1»), - положительный фронт.

Таблица 4.2

Режим Режим |

Входы | Выходы | |||||||||||||

| C | R | S0 | S1 | DSR | DSL | Dn | Q0 | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Q7 | |

| Сброс | X | L | X | X | X | X | X | L | L | L | L | L | L | L | L |

Хранение Хранение |

H | L | L | X | X | X | Q0 | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Q7 | |

Сдвиг влево Сдвиг влево |

H H | H H | L L | X X | L H | X X | Q1Q1 | Q2Q2 | Q3Q3 | Q4Q4 | Q5Q5 | Q6Q6 | Q7Q7 | L H | |

Сдвиг вправо Сдвиг вправо |

H H | L L | H H | L H | X X | X X | L H | Q0Q0 | Q1Q1 | Q2Q2 | Q3Q3 | Q4Q4 | Q5Q5 | Q6Q6 | |

Параллельная загрузка Параллельная загрузка |

H | H | H | X | X | Dn | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

см. счетчики цифровые , суммирующие счетчики , реверсивные счетчики , вычитающие счетчики ,

Распределители тактов тоже относятся к разряду счетчиков, но в отличие от счетчиков, рассмотренных ранее, особенностью этих счетчиков является то, что код, записанный в его разряды, не является двоичным, т.е. это счетчики с недвоичным кодированием. Наибольшее практическое значение среди таких счетчиков имеют счетчики с кодом «1 из N» или распределители тактов и счетчики Джонсона.

Основной областью применения распределителей тактов являются системы синхронизации и управления. На их основе получают импульсные последовательности с заданными временными диаграммами. Для этого можно вначале разбить период временной диаграммы на части («кванты»), соответствующие минимальному интервалу временной диаграммы, применив задающий генератор с частотой m/T, где m – число квантов в периоде T диаграммы. Выходные импульсы задающего генератора затем распределяются во времени и пространстве так, что каждый квант появляется в свое время и в своем пространственном канале.

На рисунке 4.38.а представлена структура распределителя тактов (РТ), согласно которой РТ имеет 1 вход, на который подаются импульсы с задающего генератора (ЗГ), и N выходов, причем первый импульс генератора передается на первый выход (канал) РТ, второй – на второй и т.д.

Рис. 4.38 Структура распределителя тактов (а) и временные диаграммы распределения уровней (б) и импульсов (в)

Распределители тактов бывают двух типов: распределители уровней (РУ) и распределители импульсов (РИ).

Временная диаграмма работы распределителя уровней представлена на рис. 4.38.б. Как видно из этой диаграммы паузы между активными состояниями каналов РУ отсутствуют.

Временные диаграммы, представленные на рис. 4.38.в, соответствуют работе распределителя импульсов. В данном распределителе тактов на выходе каждого канала появляется импульс, длительность которого соответствует длительности входных импульсов от ЗГ. Распределители импульсов не имеют самостоятельной схемотехники, они реализуются на основе распределителей уровней путем включения в их выходные цепи конъюнкторов, на вторые входы которых подаются импульсы задающего генератора.

Имея распределенные во времени и пространстве «кванты», можно по схемам ИЛИ собирать из них импульсные последовательности с необходимыми временными диаграммами. Часто нужны именно те последовательности, которые вырабатываются непосредственно распределителями тактов.

В общем случае распределители тактов могут быть получены в виде сочетания обычного двоичного счетчика и дешифратора. Такое решение наиболее очевидно. При большом числе выходных каналов эта структура может выигрывать у других, но при малом числе каналов преимущество по аппаратурной сложности и быстродействию, как правило, оказывается на стороне вариантов с кольцевыми регистрами или счетчиками Джонсона.

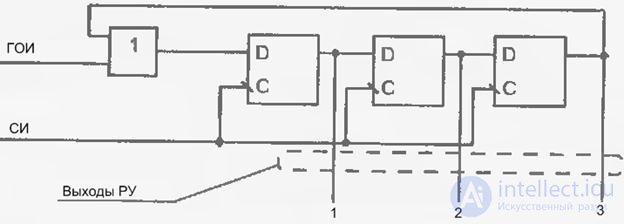

Одним из вариантов схемотехнического решения распределителя тактов, а точнее – распределителя уровней, является сдвигающий регистр, замкнутый в кольцо (кольцевой регистр сдвига), если записанное в этот регистр слово содержит всего одну единицу. При сдвигах единица перемещается с одного выхода на другой, циркулируя в кольце. Число выходов РТ равно разрядности регистра. На рис. 4.39 представлена структурная схема РТ на 3 выхода, в виде кольцевого регистра сдвига, созданного на синхронных D-триггерах.

Рис. 4.39. Структурная схема РТ на базе кольцевого регистра сдвига

Недостаток данной схемы состоит в потере правильного ее функционирования при сбое. Т.е. если в силу каких-либо причин слово (только одна единица) в регистре исказится, то возникшая ошибка будет постоянной, а это значит, что данная схема не обладает свойством самозапуска.

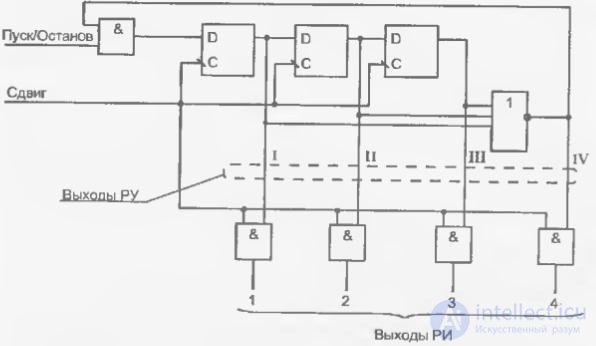

На рис. 4.40 представлена схема РТ на кольцевом регистре сдвига с самовосстановлением за несколько тактов. Работа этой схемы основана на том, что на вход регистра подаются нули, пока в нем имеется хотя бы одна единица. Таким образом, лишние возникшие единицы на его входе будут устранены и, когда регистр очистится, сформируется сигнал записи единицы на его входе. Следовательно, потеря единственной единицы также будет исключена. Выход ЛЭ, выполняющего самовосстановление схемы, дает еще один дополнительный канал. На схеме, приведенной на рис. 4.40, показаны также цепи пуска/останова РТ и два варианта выхода – для распределителя уровней (непосредственно с триггеров и ЛЭ ИЛИ-НЕ) и распределителя импульсов (после стробирования сигналов распределителя уровней импульсами сдвига на цепочке конъюнкторов).

Рис. 4.40. Схема распределителя тактов с автоматическим вхождением в рабочий цикл

Можно поставить задачу более быстрого исправления сбоев, в том числе в ближайшем такте. Для этого необходимо задать и реализовать соответствующую диаграмму состояний распределителя. Сделаем это для трехканального распределителя. Диаграмма состояний с указанием рабочего цикла кружками и ложных состояний прямоугольниками приведена на рис. 4.41. Ей соответствует таблица истинности – табл. 4.7.

Рис. 4.41. Диаграмма состояний РТ с автоматическим вхождением в рабочий цикл за один такт

Таблица 4.7

| Q1 | Q2 | Q3 | Q1H | Q2H | Q3H | Q1 | Q2 | Q3 | Q1H | Q2H | Q3H |

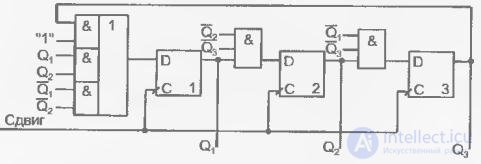

Выбрав для построения схемы D-триггеры, учтем, что функция возбуждения этого триггера D=QH. Исходя из таблицы истинности, для функций Di=QiH имеем следующие соотношения:

,

,  и

и  .

.

Схема распределителя тактов с автоматическим вхождением в рабочий цикл за один такт представлена на рис. 4.42.

Рис. 4.42. Функциональная схема распределителя тактов с автоматическим вхождением в рабочий цикл за один такт

Распределители на кольцевых регистрах сдвига находят применение при малом числе выходных каналов, когда необходимость иметь по триггеру на каждый канал не ведет к чрезмерно большим аппаратурным затратам. Достоинством таких распределителей является отсутствие дешифраторов в их структуре и, как следствие, высокое быстродействие (задержка перехода в новое состояние равна времени переключения триггера).

см счетчики цифровые , суммирующие счетчики , реверсивные счетчики , вычитающие счетчики ,

Надеюсь, эта статья про схемотехника цифровых элементов, была вам полезна, счастья и удачи в ваших начинаниях! Надеюсь, что теперь ты понял что такое схемотехника цифровых элементов, последовательностные цифровые схемы, триггеры, регистры , распределители тактов и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Компьютерная схемотехника и архитектура компьютеров

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров