Лекция

Это продолжение увлекательной статьи про схемотехника комбинационных узлов.

...

когда заранее известно количество выходов, которые нужно объединять. Часто это неизвестно. Более того, часто количество объединяемых микросхем изменяется в процессе эксплуатации устройств. Наиболее яркий пример - это компьютеры, в которых в процессе эксплуатации изменяется объем оперативной памяти, количество портов ввода-вывода, количество дисководов. В таких случаях невозможно для объединения нескольких выходов воспользоваться логическим элементом "ИЛИ". Одним из вариантов решения этой проблемы является использование микросхем, имеющих выходы с открытым коллектором. Недостатком такого объединения нескольких микросхем на один провод является низкая скорость передачи информации, обусловленная затягиванием переднего фронта.

Эта проблема исчезает, если для объединения выходов применить элементы, имеющими выходы с тремя состояниями. Такие элементы называются шинными формирователями.

Основное назначение шинных формирователей – увеличение нагрузочной способности шин в микропроцессорных и других цифровых устройствах, отключение источников и приемников информации от шин за счет наличия третьего состояния, обеспечение двунаправленного обмена информацией.

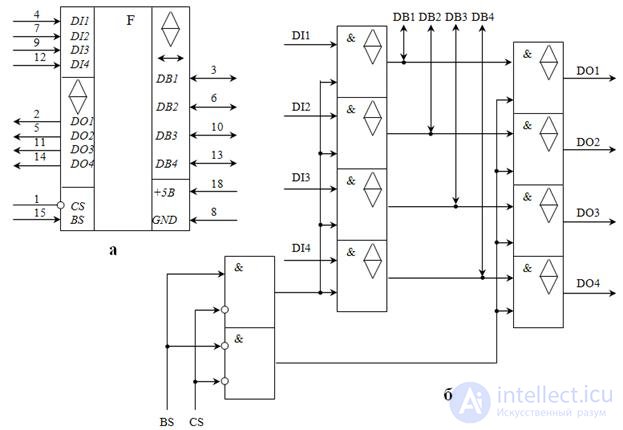

На рис. 3.12,б представлена функциональная схема шинного формирователя (ШФ) на микросхеме К589АП16, представляющая собой четырехбитную двунаправленную схему, каждая линия которой содержит две логические схемы И с мощным выходом и тремя логическими состояниями. С одной стороны входы и выходы схем И объединены (DB1…DB4) и используются для интерфейса формирователя со схемами, совместимыми с ТТЛ. С другой стороны входы DI1…DI4 и выходы DO1…DO4 разделены для максимальной гибкости использования кристалла.

Назначение входов и выходов кристалла следующие: DI1…DI4 –информационныевходы,DO1…DO4 – информационные выходы, DB1…DB4 – информационные входы-выходы реверсивной передачи информации; CS – выбор кристалла; BS – вход управления передачей информации. Если внимательно посмотреть на представленную функциональную схему шинного формирователя, то нетрудно рассмотреть, что данная схема представляет собой мультиплексор с двумя входами: DI и DB, выходомDOи управляющим сигналом BS. Режимы работы ШФ К589АП16 сведены в таблице 3.7.

Рис. 3.12. Условное обозначение (а) и функциональная схема (б) шинного формирователя К589АП16

Таблица 3.7 Режимы работы ШФ К589АП16

|

Логическое состояние по входам логики управления |

Направление передачи информации |

|

|

CS |

BS |

|

|

0 |

0 |

Передача от входов DI на выходы DB |

|

0 |

1 |

Передача от входов DB на выходы DO |

|

1 |

X |

Отсутствие передачи (высокоинпедансное состояние) |

Кроме коммутационных функций, мультиплексоры позволяют реализовать комбинационные устройства на m (m – количество управляющих входов) входов и на один выход. Если комбинационное устройство, построенное на базе мультиплексора, не требует подключения дополнительных элементов логики, то оно называется универсальным логическим модулем (УЛМ). Отметим, что мультиплексор 8®1 (3 управляющих и 8 информационных входов) позволяет реализовать любую функцию трех переменных.

Для получения УЛМ управляющие входы мультиплексора представляют как информационные, а информационные входы - как настроечные (следовательно, у мультиплексора 8 ®1 будут три информационных и 8- настроечных входов).

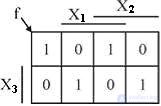

Пусть функция задана в виде карты Карно (рис. 3.13).

Рис. 3.13. Карта Карно функции, реализуемой мультиплексором

При построении УЛМ на карте Карно минимизационные контуры не проводятся. По карте записывается СHДФ с учетом состояния информационных (настроечных) входов мультиплексора.

Сопоставляя полученную СHДФ с формулой мультиплексора (3.8), определяем номера коэффициентов “а”, т.е. D0=a1, D3=a2, D5=a3, D6=a4. Следовательно, эти коэффициенты равны единице, т.е. D0 = D3 = D5= D6 = 1, а на остальных настроечных входах логические нули, т.е. D1 = D2 = D4 = D7 = 0.

Схема комбинационного устройства, построенного на базе мультиплексора 8-1 и реализующего функцию f , приведена на рис. 3.14.

Рис. 3.14. Схема соединения настроечных входов мультиплексора, реализующую функцию f

Как следует из рис. 3.14, построение комбинационного устройства на базе мультиплексора сводится к объединению настроечных входов так, чтобы получилось две группы. К одной группе входов, в соответствии с заданной функцией, подают логический “0”, а другой - “1”.

На базе мультиплексоров можно синтезировать комбинационные устройства, которые могут реализовать функции на большее число переменных, чем количество управляющих входов мультиплексора. Очевидно, и в этом случае, мультиплексор сохраняет свою универсальность, так как часть переменных реализуемой функции непосредственно подается на входы Х1 . . . Хm мультиплексора (количество переменных, непосредственно подаваемых на управляющие входы мультиплексора равно m).

Часто использование мультиплексора при синтезе КУ, реализующего функцию с числом переменных больше, чем число управляющих входов мультиплексора, существенно упрощает этот процесс и схему.

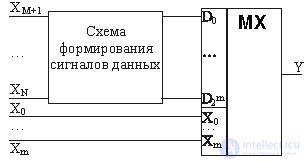

В общем случае, когда требуется синтезировать КС, реализующее функцию Nаргументов на мультиплексоре с M управляющими входами и 2М информационными входами, М младших переменных из набора Х1, Х2, ... ХN следует подать на управляющие входы, а информационные сигналы (настроечные) D0, D1, . . . . D2м нужно представить функциями остальных (N - M) переменных, как показано на рис. 3.15. Тогда синтез КС сводится, по сути дела, к синтезу схемы формирования информационных сигналов, которую можно рассматривать как внутреннюю более простую КС.

Рис. 3.15. Общая схема комбинационного устройства на мультиплексоре, реализующего функцию N переменных

Компараторы – это КС, осуществляющие сравнение (от англ. Compare – сравнение) поступающих на их вход двоичных кодов. Результатом такого сравнения могут быть следующие значения выходного сигнала: „А=В” (равенство кодов АиВ), „А≠В”(неравенство кодов АиВ) и „А<В” (код А меньше кода В) или „А>В”(код Абольше кода В), в случае „≠”.

Пусть заданы две совокупности переменных ν′=(xn, …, xp, …, x1) и ν′′=(yn, …, yp, …, y1). Так как xp=0 или 1 и yp=0 или 1, то каждая из совокупностей переменных ν′ и ν′′ имеет 2n комбинаций значений. Для краткости такие совокупности значений переменных принято называть кодами, а величины xp и yp – разрядами кодов.

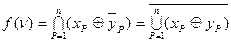

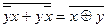

КС, реализующая функцию f(ν)=f(ν′, ν′′), где ν=( xn, …, x1, yn, …, y1), которая равна 1 только при xp=yp для всех p=1…n, называется схемой равнозначности кодов. Разряды xp и yp равны только в том случае, если  , поэтому функция

, поэтому функция  (здесь знак

(здесь знак  соответствует логической функции «И», а

соответствует логической функции «И», а – функции «ИЛИ») принимает значение, равное 1, только при по - парном равенстве всех одноименных кодов. На рис. 3.16,а и 3.16,б показаны две схемы, реализующие функцию f(ν), которые построены для n=4 на основании полученного выражения. Схема равнозначности упрощается при использовании ЛЭ «исключающее ИЛИ» с открытым коллектором (рис. 3.16, в)).

– функции «ИЛИ») принимает значение, равное 1, только при по - парном равенстве всех одноименных кодов. На рис. 3.16,а и 3.16,б показаны две схемы, реализующие функцию f(ν), которые построены для n=4 на основании полученного выражения. Схема равнозначности упрощается при использовании ЛЭ «исключающее ИЛИ» с открытым коллектором (рис. 3.16, в)).

Рис. 3.16 Схемы равнозначности кодов

Схемы сравнения двоичных чисел – это устройства, формирующие на своем выходе, помимо сигнала равенства входных кодов (А=В), еще и сигналы, несущие информацию какое из входных кодов больше другого (А<В и А>В).

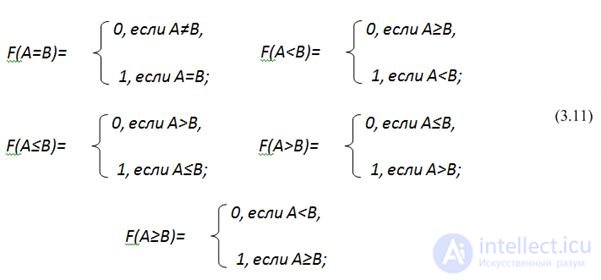

Пусть заданы два n–разрядных числа A=(xn, …, x1) и B=(yn, …, y1), где xn и yn – старшие разряды этих чисел. Соотношение между числами A и B описываются пятью функциями:

Легко заметить, что можно рассматривать только две функции, к примеру, F(A) иF(A=B), т.к. остальные функции можно выразить через них.

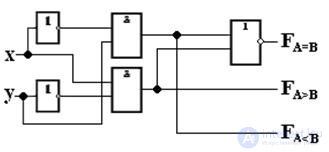

Для построения компаратора с тремя выходами (=, >и<) для одноразрядных слов (табл. 3.8) требует реализации функций: FA=B= , FA>B=

, FA>B= и FA<B=

и FA<B= . Функциональная схема компаратора для одноразрядных слов с тремя выходами представлена на рис. 3.17.

. Функциональная схема компаратора для одноразрядных слов с тремя выходами представлена на рис. 3.17.

Табл.3.8 Таблица истинности для компаратора

Рис.3.17 Функциональная схема компаратора для одноразрядных слов

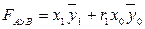

Функцию FA>B для многоразрядных слов можно получить на основе рассуждений, например, при сравнении двухразрядных слов. Если старшие разряды xiи yi не равны, то результат известен независимо от младших разрядов: при xi=1 и yi=0 имеем A>B, а приxi=0 и yi=1 имеем A. Если старшие разряды равны (xi=yi), результат неизвестен, и требуется анализ следующего разряда по тому же алгоритму. Таким образом, для двухразрядных слов можно записать:  .

.

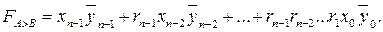

Аналогичны рассуждения для слов любой разрядности – к анализу следующего разряда нужно переходить только при равенстве предыдущих. Для n-разрядных слов:

(3.12)

(3.12)

Пример реализации компаратора с тремя выходами для двухразрядных слов приведен на рисунке 3.18. Выработка признака A>B в этой схеме производится по соотношению 3.13 (штрихом отмечены соответствующие выходы компаратора младшей группы):

(3.13)

(3.13)

Рис.3.18 Компаратор для двухразрядных слов

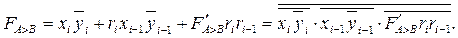

В сериях цифровых элементов представлены компараторы с тремя выходами (=, >, <). Условное графическое обозначение такого компаратора приведено на рисунке 3.19.

Рис. 3.19. Условное графическое обозначение четырехразрядного

компаратора с тремя выходами

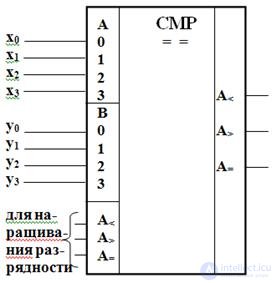

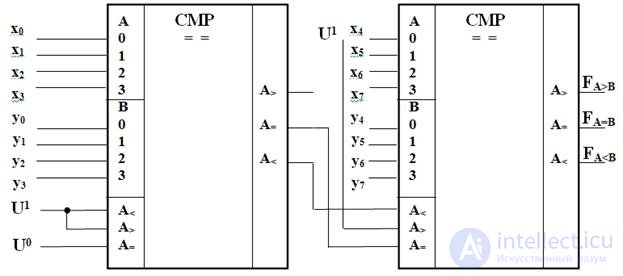

На рисунке 3.20 представлено каскадное соединение компараторов для сравнения двух восьмиразрядных чисел. При этом соединении выходы А=В, А<В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А=В, А<В и А>В микросхемы младших разрядов подают соответственно сигналы U0, U1, U1 (U0 соответствует уровню лог.”0”, U1 – лог.”1”). В последующих микросхемах на вход А>В подается сигнал U1.

Рис. 3.20. Схема каскадного соединения компараторов

Представленная на рис. 3.20 схема каскадирования компараторов обладает существенным недостатком, состоящим в увеличении задержки распространения сигнала при увеличении разрядности сравниваемых кодов. Если нам важен только факт равенства или неравенства входных кодов, то увеличить быстродействие при объединении компараторов можно, если подавать их выходные сигналы на элемент И (рис. 3.21). В этом случае суммарная задержка схемы превысит задержку одного компаратора всего лишь на задержку элемента И. При применении компараторов с инверсным выходом надо брать элемент ИЛИ с нужным числом входов.

Рис. 3.21. Уменьшение задержки при каскадировании компараторов

Сумматор – операционный элемент ЭВМ, представляющий собой схему, выполняющую арифметическое сложение и вычитание цифровых кодов двух чисел.

По способу обработки многоразрядных чисел различают сумматоры последовательные,параллельные и параллельно-последовательные.

Последовательные сумматоры строятся на основе одноразрядных сумматоров и применяются для сложения последовательных двоичных кодов. Параллельныйn-разрядный сумматор строят из n одноразрядных сумматоров по каскадному принципу, при этом обработка суммирования чисел производится одновременно во всех разрядах. Проектирование многоразрядного сумматора в этом случае сводится к синтезу одноразрядного сумматора и организации цепей переноса между разрядами в соответствии с требованиями по быстродействию.

Спустя время суммированияТсм после подачи слагаемых на выходе сумматора формируется многоразрядный результат. Время суммирования зависит как от среднего времени задержки распространения сигнала в используемых логических элементах Тлэ, так и от организации цепей переноса в сумматоре.

Одноразрядный полный сумматор имеет три входа (два слагаемых и перенос из предыдущего разряда) и два выхода (суммы и переноса в следующий разряд).

Таблица истинности (табл.7.2) одноразрядного сумматора имеет вид:

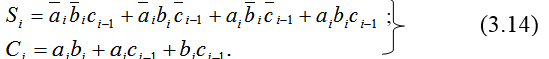

Логические зависимости (3.14), формируемые по таблице истинности, представляют собой канонические уравнения сумматора:

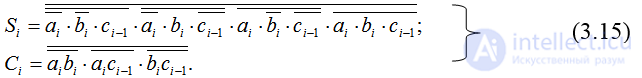

В базисе И-НЕ (штрих Шеффера) логические зависимости (3.14) имеют вид (3.15):

Непосредственное воспроизведение полученных формул на элементах двухступенчатой логики И-ИЛИ-НЕ приводит к применению элемента 2-2-2И-ИЛИ-НЕ для выработки сигнала переноса  и элемента 3-3-3-3И-ИЛИ-НЕ для сигнала

и элемента 3-3-3-3И-ИЛИ-НЕ для сигнала  Однако, наилучшее решение, приводящее к некоторому сокращению аппаратной сложности схемы при сохранении минимальной задержки по цепи переноса, получается при использовании полученного значения

Однако, наилучшее решение, приводящее к некоторому сокращению аппаратной сложности схемы при сохранении минимальной задержки по цепи переноса, получается при использовании полученного значения  в качестве вспомогательного аргумента при вычислении

в качестве вспомогательного аргумента при вычислении  .

.

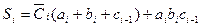

Из таблицы 3.9 следует, что во всех строчках, кроме первой и последней,  Чтобы сделать эту формулу справедливой для первой и последней строчек, необходимо убрать единицу в строчке нулевых входных величин и добавить единицу в строчку единичных входных величин. Такая операция приводит к соотношению (3.16).

Чтобы сделать эту формулу справедливой для первой и последней строчек, необходимо убрать единицу в строчке нулевых входных величин и добавить единицу в строчку единичных входных величин. Такая операция приводит к соотношению (3.16).

(3.16)

(3.16)

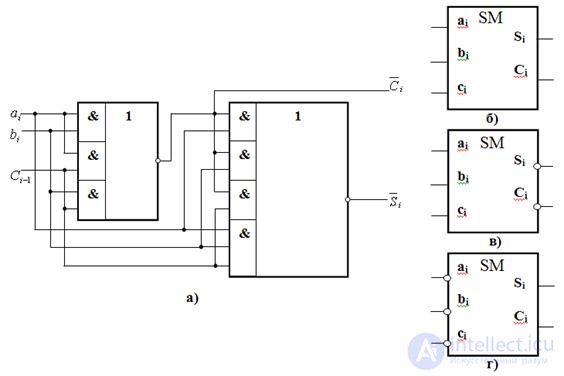

Схема сумматора, построенного по соотношению (3.16), приведена на рисунке 3.22.

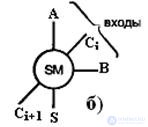

Рис. 3.22. Схема функциональная (а) и условные графические обозначения (б, в, г) полного одноразрядного сумматора

Для сложения двух n-разрядных двоичных чисел А и В необходимо использовать n-одноразрядных полных сумматоров. При этом могут применяться два способа суммирования – последовательное и параллельное. Использование того или иного способа суммирования зависит от характера ввода/вывода чисел и организации переносов в многоразрядном сумматоре.

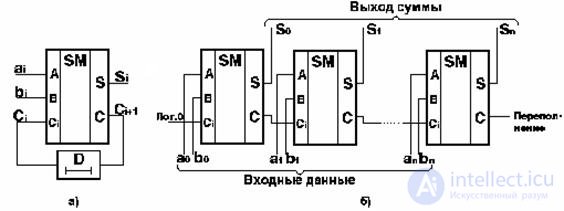

Последовательный сумматор (рис. 3.23,а) суммирует двоичные числа, поступающие с определенным тактом, поразрядно, начиная с младшего разряда, с помощью полного одноразрядного сумматора. Сформированный в данном разряде перенос Ci+1 с помощью схемы задержки задерживается на один такт следования разрядов и подается на входСiсумматора в момент поступления последующего разряда. Сложив младшие разряды, многоразрядный сумматор вырабатывает сумму для младшего разряда результата и перенос, который задерживается на один такт. В следующем такте складываются вновь поступившие разряды слагаемых aiиbiс переносом из младшего разряда и т.д.

Рис. 3.23. Схемы функциональные последовательного (а) и параллельного (б) сумматоров

Параллельный сумматор суммирует два многоразрядных числа одновременно во всех разрядах и характеризуется разными способами передачи переносов от младших разрядов к старшим. Схема функционирования многоразрядного параллельного комбинационного сумматора составляется из одноразрядных и имеет вид, представленный на рисунке 3.23,б. Суммирование во всех разрядах, начиная с младшего, происходит по единым правилам. В каждом i-ом разряде осуществляется сложение ai+bi+ci-1. Результат представляется кодами суммы Siи переносаCi.

Для увеличения быстродействия многоразрядных сумматоров, получаемых последовательным включением одноразрядных сумматоров, необходимо уменьшить время распространения сигнала переноса от входа до выхода.

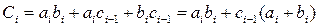

Вследствие большой сложности создания сумматоров с параллельным переносом для n-разрядов, их в чистом виде практически не используют. Однако, принцип параллельного переноса используется в сумматорах с групповым (параллельно-последовательным)переносом. Принцип которого поясняется нижеследующим:

Из (3.14) следует  , или

, или  , если в данном выражении принять, что

, если в данном выражении принять, что  , а

, а  . В таком случае для 4-х разрядного сумматора функция выхода переноса из старшего (четвертого) разряда будет иметь следующий вид:

. В таком случае для 4-х разрядного сумматора функция выхода переноса из старшего (четвертого) разряда будет иметь следующий вид:

.(3.17)

.(3.17)

Если внутренние переносы в таком сумматоре реализовать логикой, функционирующей в соответствии с (3.17), то такой сумматор называется сумматором с параллельным переносом, в отличие от сумматора с последовательным переносом, блок-схема которого изображена на

рис. 3.23,б.

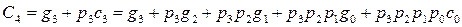

Рис. 3.24 Блок-схема четырехразрядного параллельного сумматора со схемой параллельного формирования переноса (а) и ИМС 555ИМ6 с нумерацией выходов (б)

На рис. 3.24,а представлена структурная схема 4-х разрядного сумматора с параллельным переносом, где CRU – Carry Unit (устройство переноса). На рис. 3.24,б представлено графическое обозначение микросхемы переноса 555ИМ6.

Таким образом, параллельный сумматор с групповым переносом образуется из n-разрядного сумматора, имеет N групп, в границах каждой из которых формирование переноса осуществляется одновременно, без задержки от разряда к разряду. Выход переноса от младшей группы разрядов является одним из составляющих для формирования сигнала переноса в очередную старшую группу. Т.е. задержка формирования переноса на выходе сумматора будет определяться суммарной задержкой формирования переносов в N группах. В сравнении с обычным сумматором, в сумматоре с групповым переносом достигается большее быстродействие.

Сумматор может вычислять не только сумму, но и разность входных кодов, то есть работать вычитателем. Для этого вычитаемое число надо просто поразрядно проинвертировать, а на вход переноса С подать единичный сигнал (рис. 3.25).

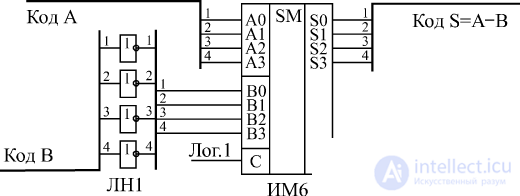

Рис. 3.25 4-х разрядный вычитатель на сумматоре ИМ6 и инверторах ЛН1

Для выполнения над операндами А и В как арифметических, так и логических операций используются микросхемы универсальных арифметико-логических устройств (АЛУ). Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности АЛУ и обеспечивающей его перестройку с одной операции на другую.

Наиболее часто АЛУ четырехразрядные и для наращивания разрядности они объединяются с формированием последовательных или параллельных переносов. Логические возможности АЛУ разных технологий (ТТЛШ, КМОП, ЭСЛ) сходны.

В зависимости от построения и характера работы различают АЛУ последовательного, параллельного и параллельно – последовательного действия. В АЛУ последовательного действия операции над кодами осуществляются последовательно, разряд за разрядом. Код числа представляется в виде серии сигналов, действующих в одной и той же цепи в различные моменты времени. В АЛУ параллельного действия операции над кодами чисел осуществляются параллельно по всем разрядам. Коды чисел изображаются в виде совокупности сигналов, каждый из которых действует по своей определенной цепи. Такие АЛУ получили наиболее широкое применение. В АЛУ параллельно – последовательного действия коды чисел разбиваются на группы из определенного количества разрядов. Операции над кодами чисел внутри каждой группы осуществляются параллельно, а операции между группами разрядов осуществляется последовательно.

На рисунке 3.26 показано условное графическое обозначение АЛУ. Здесь А и В – входы операндов, S – входы выбора операций, Ci – сигнал переноса и М (Mode) – сигнал задания типа операции: М=1 соответствует логическим операциям, а М=0 – арифметическим. Результат операции выдается на выходы Y, выходы Gи Hпредназначены для выдачи значений генерации и прозрачности, используемые для организации параллельных переносов при наращивании размерности АЛУ. Сигнал Co – выход переноса, а выход A=B<> - выход сравнения на равенство с открытым коллектором.

Рис.3.26 Условное графическое обозначение АЛУ

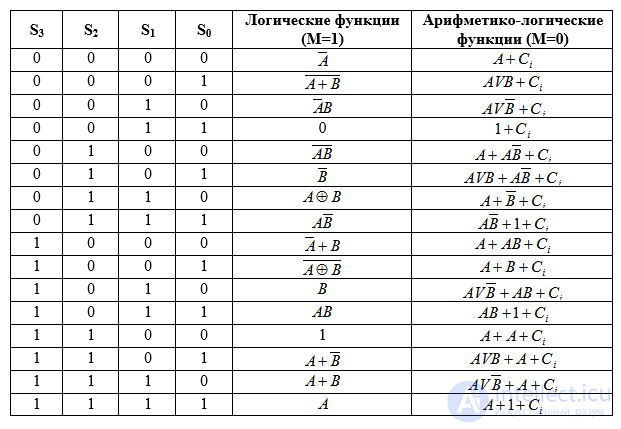

В таблице 3.10 приведен перечень операций, выполняемых АЛУ. Шестнадцать логических операций позволяют воспроизводить все функции двух переменных. В арифметико-логических операциях встречаются операции, являющиеся и логическими и арифметическими одновременно.

Запись  означает: вначале поразрядно выполняются операции инвертирования (

означает: вначале поразрядно выполняются операции инвертирования ( ), за ней – логического сложения (

), за ней – логического сложения ( ) и умножения (

) и умножения ( ), а затем полученные результаты (

), а затем полученные результаты ( ) и (

) и ( ) складываются арифметически.

) складываются арифметически.

При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных или параллельных переносов. В последнем случае совместно с АЛУ применяют микросхемы – блоки ускоренного переноса (CRU), получающие от отдельных АЛУ сигналы генерации и прозрачности, а также входной перенос и вырабатывающие сигналы переноса.

Возможна блочная и многофункциональная структура АЛУ. В блочном АЛУ содержится набор устройств для выполнения отдельных видов операций или операций над определенными видами операндов. В многофункциональных АЛУ все операции над любыми числами выполняются в одном устройстве. Основу таких АЛУ составляют сумматоры и регистры, которые при выполнении отдельных операций коммутируются между собой определенным образом посредством групп логических элементов. АЛУ блочного типа состоят из отдельных блоков сложения, умножения, деления и т.д. Такие АЛУ имеют большее быстродействие, чем многофункциональные, однако для своей реализации требуют больше оборудования.

Таблица 3.10 Перечень операций, выполняемых АЛУ

Микросхемы множительных устройств появились в 80-х годах 20 столетия, когда достигнутый уровень интеграции позволил разместить в одном кристалле достаточно большое количество логических элементов.

Структура матричных умножителей тесно связана со структурой математических выражений, описывающих операцию умножения.

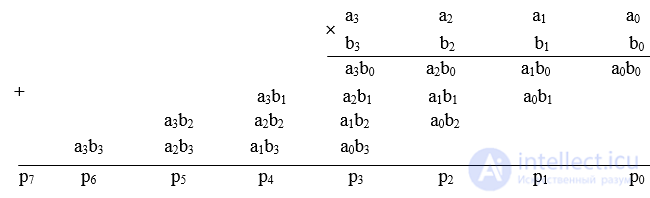

Пусть имеются два целых двоичных числа без знаков Am=am-1…a0 и Bn=bn-1…b0. Их перемножение выполняется по известной схеме «умножения столбиком». Если числа четырехразрядные, т.е. m=n=4, то

Произведение выражается числом Pm+n-1=pm+n-1 pm+n-2… p0. Члены aibj, где i=0… (m-1) и j=0… (n-1) вырабатываются параллельно во времени конъюнкторами. Их сложение в столбцах, которое можно выполнять разными способами, составляет основную операцию для умножителя и определяет почти целиком время перемножения.

Матричные перемножители могут быть просто множительными блоками (МБ) илимножительно-суммирующими (МСБ), при этом последние обеспечивают удобство наращивания размерности умножителя.

МСБ реализуют операцию P=Am×Bn+ Cm×Dn, т.е. добавляют к произведению два слагаемых: одно разрядности m, совпадающего с разрядностью множимого, другое разрядности n, совпадающей с разрядностью множителя.

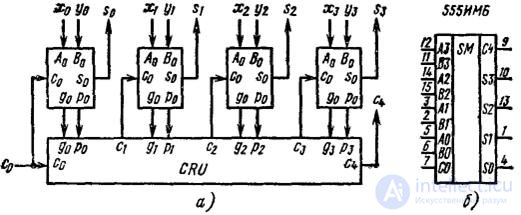

Рис.3.27 Схема множительно-суммирующего блока для четырехразрядных сомножителей (а), обозначение одноразрядного сумматора для данной схемы

Множительно-суммирующий блок для четырехразрядных операндов без набора конъюнкторов, вырабатывающих члены вида aibj, показан на

рис. 3.27,а, где для одноразрядного сумматора принято обозначение

(рис. 3.27,б).

Максимальная длительность умножения – сумма задержек сигналов в конъюнкторах для выработки членов aibj и задержки в наиболее длинной цепочке передачи сигнала в матрице одноразрядных сумматоров, равной 2n-1 (m+n-1 в общем случае). Таким образом,tМСБ=tK+(2n-1)tSM.

Построение умножителей большей размерности из умножителей меньшей размерности на основе МСБ предполагает нахождение частичных произведений и дальнейшее их сложение с учетом взаимного положения (сдвига одного относительно другого).

В задачу синтеза любых цифровых схем, в том числе и комбинационных, входит построение принципиальной схемы устройства, реализующего заданные условия его работы с учетом заданного базиса элементов. Задание комбинационного узла сводится к заданию тех функций, которые он должен реализовать. Число функций определяется только числом выходов разрабатываемого комбинационного узла.

Процесс синтеза КУ состоит из 2-х этапов:

1. Абстрактный синтез, который включает:

2. Схемный синтез, в процессе которого осуществляется:

По завершении испытаний и анализа их результатов может потребоваться корректировка схемы. Завершается синтез подготовкой технической документации.

В практике проектирования ЭВМ накоплен огромный опыт по синтезу различных схем. Общая постановка задачи структурного синтеза комбинационных схем (КС) заключается в построении оптимального проектируемого устройства, моделирующего закон функционирования цифрового устройства без памяти, представленного одной булевой функцией или системой булевых функций.

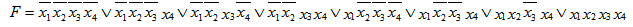

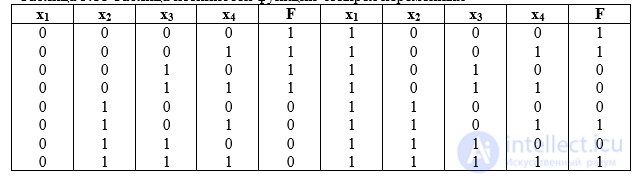

Существует множество способов задания законов функционирования цифровых устройств комбинационного типа, но чаще всего для этого пользуются таблицами функционирования (таблицами истинности), задающими значения искомых функций на всех наборах входных аргументов. От таблицы истинности легко перейти к искомой функции в совершенной дизъюнктивной нормальной форме (СДНФ). Для этого составляется логическая сумма тех наборов аргументов, на которых функция принимает единичное значение. Например, для подлежащей воспроизведению функции четырех аргументов, заданной в табл. 3.11, получим:

Таблица 3.11 Таблица истинности функции четырех переменных

Дальнейшие действия зависят от средств реализации функций, к которым в современной схемотехнике относятся:

продолжение следует...

Часть 1 Тема 3. Схемотехника комбинационных узлов

Часть 2 3.6 Синтез КС на основе мультиплексоров - Тема 3. Схемотехника

Часть 3 3.11.2 Основные факторы, которые должны быть учтены при построении принципиальных

Комментарии

Оставить комментарий

Компьютерная схемотехника и архитектура компьютеров

Термины: Компьютерная схемотехника и архитектура компьютеров