Лекция

Контроль четности – это один из методов обнаружения ошибок при передаче данных в цифровых системах. Он широко используется в вычислительных устройствах, сетевых протоколах и системах связи для обеспечения достоверности информации. Основной принцип работы контроля четности заключается в добавлении контрольного бита к передаваемым данным, что позволяет проверять их целостность. Системы контроля четности бывают разных типов, включая четную и нечетную проверку, а также расширенные методы, использующие циклическое избыточное кодирование.

Данные узлы служат для определения четности количества единиц, либо нулей в многоразрядных двоичных словах. Если их число четное, то устройство вырабатывает на выходе определенный сигнал, например логический ноль, в противном случае – единицу. Таким образом, результатом обработки слова 101100011101 будет 1, а для 1100101 – ноль.

Такие устройства находят широкое применение в системах передачи цифровых данных для обнаружения ошибок.

Операция контроля четности двоичных чисел позволяет повысить надежность передачи и обработки информации. Ее сущность заключается в суммировании по модулю 2 всех разрядов с целью выяснения четности числа, что позволяет выявить наиболее вероятную ошибку в одном из разрядов двоичной последовательности. Например, если при передаче кода 1001 произойдет сбой во втором разряде, то на приемном пункте получим код 1101 — такую ошибку определить в общем случае затруднительно. Если же код относится к двоично-десятичному (8-4-2-1), то ошибку легко обнаружить, поскольку полученный код (десятичный эквивалент — число 13) не может в принципе принадлежать к двоично-десятичному.

Обнаружение ошибок путем введения дополнительного бита четности происходит следующим образом. На передающей стороне передаваемый код анализируется и дополняется контрольным битом до четного или нечетного числа единиц в суммарном коде. Соответственно суммарный код называется четным или нечетным. В случае нечетного кода дополнительный бит формируется таким образом, чтобы сумма всех единиц в передаваемом коде, включая контрольный бит, была нечетной. При контроле четности все, естественно, наоборот. Например, в числе 0111 число единиц нечетно. Поэтому при контроле нечетности дополнительный бит должен быть нулем, а при контроле четности — единицей. На практике чаще всего используется контроль нечетности, поскольку он позволяет фиксировать полное пропадание информации (случай нулевого кода во всех информационных разрядах). На приемной стороне производится проверка кода четности. Если он правильный, то прием разрешается, в противном случае включается сигнализация ошибки или посылается передатчику запрос на повторную передачу.

Схема формирования бита четности для четырехразрядного кода показана на рис. 9.25. Она содержит четыре элемента Исключающее ИЛИ, выполняющих функции сумматоров по модулю 2 (без переноса) и состоит из трех ступеней. На первой ступени попарно суммируются все биты исходного кода на входах А, В, С, D. На второй ступени анализируются сигналы первой ступени и устанавливается четность или нечетность суммы входного кода. На третьей ступени полученный результат сравнивается с контрольным сигналом на входе Е, задающим вид используемого контроля, в результате чего на выходе F формируется пятый дополнительный бит четности, сопровождающий информационный сигнал в канале передачи.

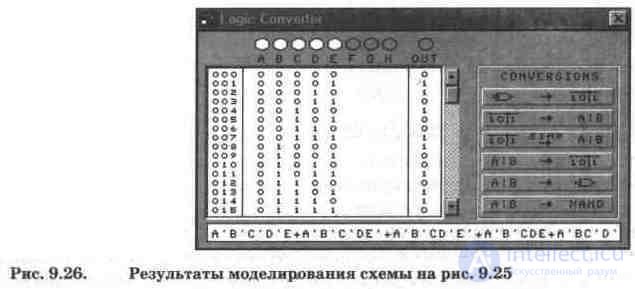

Результаты моделирования формирователя показаны на рис. 9.26 в виде таблицы истинности из 32 возможных двоичных комбинаций и булева выражения (из 32 комбинаций на рис. 9.26 видны только первые 16, остальные просматриваются с помощью линейки прокрутки). Для просмотра составляющих булева выражения необходимо мышью поместить курсор в дополнительный дисплей и передвигать его клавишами управления курсором.

В библиотеке программы EWB схема проверки на четность и нечетность представлена ИМС 74280 (аналог — К555ИП5), схема ее включения показана на рис. 9.27. ИМС 74280 имеет 9 входов (A, B...I) и два выхода (EVEN, ODD), один из которых — инверсный. Вход I используется для управления видом контроля (0 — контроль четности, 1 — контроль нечетности) и управляется переключателем Z (управляется с клавиатуры одноименной клавишей). Вывод NC — not connection — пустой, т.е. внутри ИМС к нему ничего не подключено.

Правильность функционирования схемы на рис. 9.27 проверяется с помощью генератора слова, при этом тип контроля (четности или нечетности) выбирается переключателем Z; на входы рассматриваемого устройства подаются различные двоичные комбинации; состояние выходов ИМС контролируется подключенными к ним светоиндикаторами (логическими пробниками).

Данные узлы служат для определения четности количества единиц, либо нулей в многоразрядных двоичных словах. Если их число четное, то устройство вырабатывает на выходе определенный сигнал, например логический ноль, в противном случае – единицу. Таким образом, результатом обработки слова 101100011101 будет 1, а для 1100101 – ноль.

Такие устройства находят широкое применение в системах передачи цифровых данных для обнаружения ошибок.

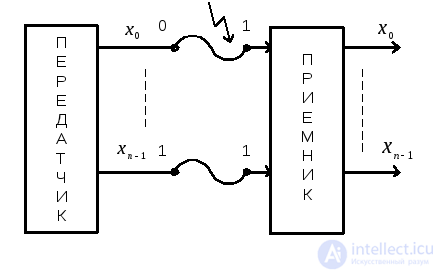

В процессе передачи данных в системе, состоящей из источника сигнала (передатчика), приемника и линии передачи из-за воздействия помех может произойти изменение значения передаваемого бита. То есть по какой-либо линии передается логический ноль, а будет принята единица, либо наоборот, что приведет к искажению полученной информации.

Т ак как передаваемые данные заранее неизвестны, то приемник воспримет полученную информацию как истинную, что может привести к существенному нарушению работы связанных с ним устройств.

ак как передаваемые данные заранее неизвестны, то приемник воспримет полученную информацию как истинную, что может привести к существенному нарушению работы связанных с ним устройств.

Однако, если появление ошибки в переданном слове удастся обнаружить, то его можно будет передать еще раз и производить эту процедуру до тех пор, пока принятое слово не окажется идентичным переданному.

В этом случае требуется введение критерия, по значению которого на принимающей стороне можно судить о наличии или отсутствии ошибки при передаче. Одним из таких критериев и является четность количества единиц в передаваемом и принятом словах. Если она при передаче не меняется, то с достаточно большой вероятностью можно считать, что и само слово не претерпело трансформации.

Данным способом можно определить одиночные ошибки, либо ошибки сразу в трех, пяти и любом нечетном количестве разрядов. Если инверсия (искажение) значений произойдет у четного их числа, то четность количества единиц в измененном слове сохранится. Так как наиболее вероятными и частыми являются одиночные ошибки, их обнаружению уделяют особое внимание.

Вариант структуры устройства, выявляющего одиночные ошибки при передаче данных, выглядит следующим образом.

На передающей стороне используется формирователь бита четности (схема контроля четности), вырабатывающий признак  , равный логическому нулю, если количество единиц в передаваемом слове четное и логической единице в противном случае. Этот бит передается вместе со всеми разрядами слова и поступает на приемник, к выходам которого подключается аналогичная схема, проверяющая на четность количество единиц в принятом совместно с дополнительным разрядом слове.

, равный логическому нулю, если количество единиц в передаваемом слове четное и логической единице в противном случае. Этот бит передается вместе со всеми разрядами слова и поступает на приемник, к выходам которого подключается аналогичная схема, проверяющая на четность количество единиц в принятом совместно с дополнительным разрядом слове.

Е сли число единиц в слове, формируемом передатчиком было четным, то бит четности равен нулю и общее количество единиц в передаваемом слове окажется четным. В случае, когда в исходном слове нечетное число единиц, бит четности примет единичное значение и общее количество единиц в передаваемом слове опять окажется четным.

сли число единиц в слове, формируемом передатчиком было четным, то бит четности равен нулю и общее количество единиц в передаваемом слове окажется четным. В случае, когда в исходном слове нечетное число единиц, бит четности примет единичное значение и общее количество единиц в передаваемом слове опять окажется четным.

Таким образом, в отсутствии помех при передаче число единиц в принятом слове всегда четно. При этом схема контроля четности будет формировать признак правильности приема, равный нулю.

Если при передаче произойдет изменение значения (инверсия) одного из разрядов, то четность числа единиц в принятом совместно с разрядом  слове окажется нарушенной. На выходе схемы контроля четности сформируется единичный сигнал, являющаяся признаком возникновения ошибки при передаче, что будет служить основанием для повторной передачи слова принятого с ошибкой.

слове окажется нарушенной. На выходе схемы контроля четности сформируется единичный сигнал, являющаяся признаком возникновения ошибки при передаче, что будет служить основанием для повторной передачи слова принятого с ошибкой.

Как уже отмечалось, когда инверсия возникает в двух разрядах, то четность числа единиц в принятом слове сохраняется, и этап передачи будет определен как безошибочный. Однако вероятность возникновения двух или более ошибок гораздо ниже, чем одиночной.

Синтез схемы контроля четности удобно начать с ее простейшего варианта для двухразрядного слова. Функция, описывающая четность количества единиц в нем, задается такой таблицей.

Так как разряды слова можно считать логическими переменными, то эта функция является одной из 16 от двух переменных, в частности – функцией логической неравнозначности. Таким образом, для контроля четности числа единиц в двухразрядном слове требуется использовать сумматор по модулю два, а алгебраически данная процедура записывается следующим образом  .

.

Для синтеза схем контроля четности в многоразрядных словах можно задать соответствующую функцию в табличной форме, затем определить ее аналитический вид и разработать схему на стандартных логических элементах. Однако такой способ является достаточно трудоемким, так как с увеличением разрядности слова на единицу, число строк таблицы удваивается. Поэтому в данной ситуации удобнее использовать нестандартный подход.

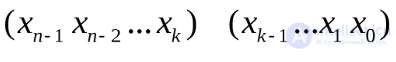

Пусть имеется n-разрядное двоичное слово  . Разобьем его на две части

. Разобьем его на две части  и предположим, что имеются устройства

и предположим, что имеются устройства  позволяющие формировать признаки четности количества единиц в них. Очевидно, что четность или нечетность числа единиц в частях слова, определенным образом зависит от ситуации с данным показателем для всего слова

позволяющие формировать признаки четности количества единиц в них. Очевидно, что четность или нечетность числа единиц в частях слова, определенным образом зависит от ситуации с данным показателем для всего слова

Это можно отразить следующим образом.

|

Количество единиц в слове |

Количество единиц в частях слова |

|

|

Четное (0) |

Четное (0) |

Четное (0) |

|

Четное (0) |

Нечетное (1) |

Нечетное (1) |

|

Нечетное (1) |

Четное (0) |

Нечетное (1) |

|

Нечетное (1) |

Нечетное (1) |

Четное (0) |

Если слово имеет четное число единиц, то при любом его разбиении в частях слова окажется по четному, либо по нечетному их количеству. При нечетном числе единиц во всем слове, в одной из его частей всегда окажется четное их количество, а в другой нечетное.

В скобках в таблице приведены значения сигналов, формируемых устройствами

скобках в таблице приведены значения сигналов, формируемых устройствами  и тех, которые должны появиться на выходе схемы контроля четности числа едини ц во всем слове. Видно, что эта таблица описывает функцию логической неравнозначности над переменными, формируемыми вспомогательными устройствами. Таким образом, структура схемы контроля четности должна иметь следующий вид.

и тех, которые должны появиться на выходе схемы контроля четности числа едини ц во всем слове. Видно, что эта таблица описывает функцию логической неравнозначности над переменными, формируемыми вспомогательными устройствами. Таким образом, структура схемы контроля четности должна иметь следующий вид.

Разбивая части слова на более мелкие компоненты и проводя аналогичные рассуждения, можно придти к выводу, что в итоге потребуется первоначальный контроль четности количества единиц лишь в двух соседних разрядах слова и дополнительная обработка полученных результатов схемами логической неравнозначности. Отсюда следует, что один из вариантов принципиальной схемы устройства контроля четности будет выглядеть следующим образом.

При синтезе такого устройства стандартным способом оно получилось бы достаточно громоздким, так как функция, описывающая его работу относится к классу неминимизируемых в базисе И-НЕ, ИЛИ-НЕ.

Промышленностью выпускаются схемы контроля четности в интегральном исполнении, в частности микросхема К155ИП2. Она обрабатывает восьмибитовые слова и имеет входы расширения, позволяющие наращивать разрядность. Аналогичные функции выполняет микросхема К1533ИП5, работающая с девятиразрядными числами.

Использование контроля четности играет важную роль в обеспечении надежной передачи информации, снижая вероятность ошибок и защищая системы от сбоев. Хотя этот метод является относительно простым, он остается эффективным для быстрого обнаружения одиночных ошибок в битах данных. В современных вычислительных и коммуникационных системах контроль четности дополняется другими механизмами проверки и исправления ошибок, что делает цифровую передачу еще более стабильной и безопасной.

1. Как называется метод контроля ошибок, основанный на добавлении дополнительного бита к данным?

2. Какой бит добавляется к данным при четном контроле четности?

3. Какой тип контроля четности используется для обеспечения нечетного количества единиц в данных?

4. Как называется устройство, которое проверяет контрольный бит в передаваемых данных?

5. Что происходит, если контроль четности обнаруживает ошибку в данных?

6. Какой логический оператор часто используется для вычисления контрольного бита?

7. Какой тип ошибки может быть обнаружен с помощью контроля четности?

8. Как называется схема, которая добавляет контрольный бит к каждому байту данных?

9. Какой недостаток есть у метода контроля четности?

10. Какой компонент используется для реализации контроля четности в цифровых схемах?

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ

Термины: Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ