Лекция

Это окончание невероятной информации про счетчики цифровые.

...

между зонами единиц и нулей (табл. 4.8).

Таблица 4.8

| Номер состояния | Q1 | Q2 | Q3 | Q4 | Номер состояния | Q1 | Q2 | Q3 | Q4 |

В двух случаях (для слов, состоящих только из нулей или только из единиц) состояние выявляется анализом крайних разрядов. В остальных случаях анализируются разряды на границе зоны единиц и нулей.

Как видно из таблицы, преобразование выходного кода счетчика Джонсона в код «1 из N» осуществляется согласно следующим выражениям:

,

,  ,

,  ,

,  ,

,

,

,  ,

,  и

и  ,

,

где Fi (i=0…7) – выходы распределителя тактов.

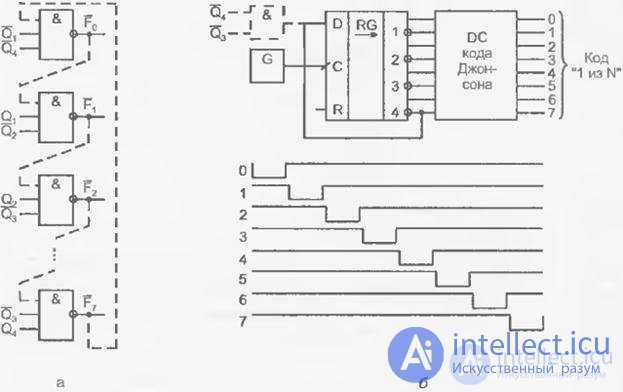

По полученным выражениям строится дешифратор. Рассмотрим дешифратор на ЛЭ И-НЕ (с инверсными выходами). В таком дешифраторе можно дополнительно принять меры по предотвращению перекрытий импульсов в соседних каналах, возможных из-за различных задержек элементов. Используя элементы с тремя входами и «косыми связями» (рис. 4.44.а) можно запретить начало импульса в последующем канале до его завершения в предыдущем.

Рис. 4.44. Функциональная схема дешифратора кода Джонсона в код «1 из N» (а), структурная схема распределителя тактов на основе счетчика Джонсона и временные диаграммы его работы (б)

Распределитель тактов в целом (рис. 4.44.б) имеет выходные сигналы в коде «1 из N».

Для схем со счетчиком Джонсона могут возникнуть вопросы преодоления ограничения обязательной четности числа состояний счетчика и обеспечения автоматического вхождения его в рабочий цикл (свойства самозапуска).

Первую задачу можно решить в рамках подхода, применявшегося при построении счетчиков с произвольным модулем, т.е. исключением одного «лишнего» состояния. Получить схему с исключенным состоянием можно уже не раз показанным способом, переходя от таблицы функционирования (истинности) к функции возбуждения триггеров и далее к схеме. Однако в данном случае нетрудно сократить этот путь, воспользовавшись простыми рассуждениями. Пусть исключению подлежит состояние 11..11. Чтобы его исключить необходимо перейти к следующему состоянию не из состояния «все единицы», а от предыдущего состояния 11…10, которое создает единицу в предпоследнем разряде счетчика, т.е. ноль на инверсном выходе этого разряда. Подавая нулевой сигнал на вход счетчика вместе с основным сигналом обратной связи через конъюнктор (показан на рис. 4.44.б штриховой линией) исключим состояние 11…11 и получим счетчик с нечетным числом состояний 2n-1.

Задача обеспечения вхождения распределителя на основе счетчика Джонсона в рабочий циклсвязана с тем, что базовая схема, рассмотренная выше, свойством самозапуска не обладает. Например, распределитель с трехразрядным счетчиком Джонсона имеет общее число возможных состояний 23=8, а число состояний в рабочем цикле 2×3=6. Неиспользуемыми являются два состояния: 010 и 101. Нетрудно заметить, что из состояния 010 счетчик перейдет в состояние 101, а из состояния 101 в состояние 010. Таким образом, наряду с замкнутым рабочим циклом существует цикл из двух неиспользуемых состояний, попав в который, схема без постороннего воздействия не сможет перейти в рабочий цикл.

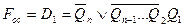

Чтобы придать схеме свойство самозапуска, нужно модифицировать сигнал обратной связи, поступающий на вход счетчика. Это можно сделать разными способами, поскольку траектория перехода из замкнутого цикла неиспользуемых состояний в рабочий неоднозначна. Одной из возможностей является выработка сигнала обратной связи согласно выражению

.

.

Распределители тактов на основе счетчика Джонсона характеризуются небольшими аппаратурными затратами (1/2 триггера и один двухвходовой вентиль на 1 канал) и достаточно высоким быстродействием (время установления = сумма задержек переключения триггера и вентиля). Счетчики Джонсона реализованы, в частности, в сериях ИС типа КМОП (микросхемы ИЕ9 и ИЕ19 серии К531 и др.), причем одной из причин их применения является отсутствие импульсных помех в цепи питания, создаваемых микросхемами. Распределитель тактов в целом реализован в ИС К561ИЕ8.

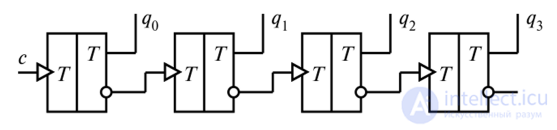

Обычно требуется посчитать большее количество импульсов. В этом случае можно использовать выходной сигнал первого счетного триггера как входной сигнал для следующего триггера, то есть соединить триггеры последовательно. Так можно построить любой счетчик, считающий до максимального числа, кратного степени два. Такой счетчик называется двоичным счетчиком, а тот факт, что состояние триггеров меняется на противоположное в различные моменты времени по мере распространения цифрового сигнала, отображается термином: асинхронный двоичный счетчик.

асинхронный счетчик — цепочка счетных триггеров, вход каждого из которых подключен к выходу предыдущего триггера. В асинхронных счетчиках под воздействием входного импульса происходит переключение соответствующих разрядов последовательно от разряда к разряду Для построения асинхронного суммирующего счетчика необходимо включить последовательно требуемое количество асинхронных триггеров с динамическим управлением (рис. 12.3). При соединении триггеров между собой необходимо учитывать вид сигнала, вызывающего изменение состояния триггера. Для того чтобы триггеры, имеющие прямой динамический вход, изменяли свое состояние по спаду входного сигнала предыдущего триггера, входы триггеров должны быть подключены к инверсным выходам предыдущих триггеров.

Рис. 12.3. Асинхронный суммирующий счетчик

Достоинством асинхронных счетчиков является простота схемы: увеличение разрядности производится подключением необходимого числа триггеров. К недостаткам асинхронных счетчиков относятся сравнительно низкое быстродействие и его зависимость от числа разрядов, а также появление промежуточных значений выходных двоичных кодов при последовательном переключении триггеров в новое состояние.

1. Определение количества разрядов счетчика и составление таблицы функционирования.

2. Определение сигналов, подаваемых на тактирующие входы триггеров.

3. Заполнение прикладных диаграмм Вейча и выделение на них ячеек соответствующих отсутствию разрешающего сигнала на

трактующих входах триггеров.

4. Заполнение диаграмм Вейча для уравнений входов с использованием прикладных диаграмм Вейча и характеристических таблиц используемых триггеров.

5. Считывание с диаграмм Вейча уравнений входов в минимизированном виде с учетом дополнительных появившихся

факультативно задаваемых значений.

6. Перевод уравнений входов в структурный вид в используемом базисе логических элементов.

7. Изображение схемы счетчика

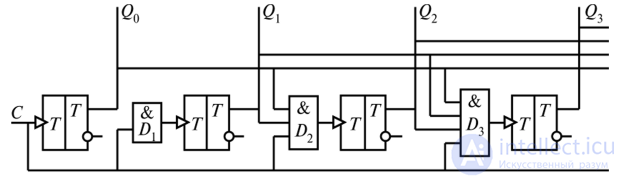

Синхронный счетчик - счетчик, в котором триггеры переходят в новые состояния одновременно (синхронно). Ко всем разрядам такого счетчика информация о состоянии предыдущих разрядов поступает параллельно, также одновременно поступают к ним счетные (входные) импульсы.

Переключение их в нужной последовательности обеспечивается логическими цепями, которые при поступлении входного импульса одни триггеры удерживают от переключения, а другим разрешают переключиться.

В синхронных счетчиках срабатывание всех триггеров происходит по фронту тактовых импульсов, которые одновременно подаются на входы с всех разрядов, а наличие или отсутствие переключения определяют управляющие входы: j, к или t. Для повышения быстродействия в схемах синхронных счетчиков используют цепи ускоренного переноса (рис. 12.6).

Рис. 12.6. Синхронный счетчик с параллельным переносом

Быстродействие увеличивается в счетчиках со сквозным переносом. Рассматривая пример суммирования двоичных чисел 00112 + + 1 = 01002, можно сделать вывод, что для получения результата необходимо инвертировать все младшие разряды, равные нулю, и первый разряд, содержащий единицу.

1. Определение количества разрядов счетчика и составление таблицы его функционирования.

2. Заполнение прикладных диаграмм Вейча.

3. Заполнение диаграмм Вейча для уравнений входов с использованием прикладных диаграмм Вейча и характеристических таблиц используемых триггеров.

4. Считывание с диаграмм Вейча уравнений входов в минимизированном виде.

5. Перевод уравнений входов в структурный вид в используемом базисе логических элементов.

6. Изображение схемы счетчика.

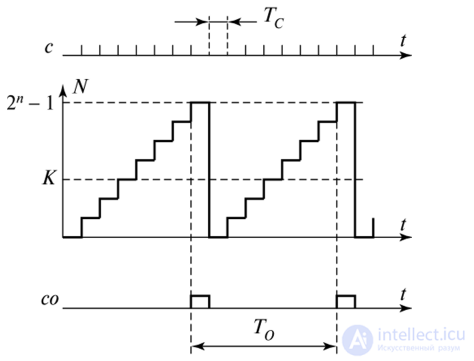

Максимальную емкость счетчика определяет модуль М=2п который выражается целой степенью числа 2. При использовании счетчика в качестве делителя частоты период повторения импульсов переполнения на выходе счетчика содержит 2п периодов входного сигнала (рис. 12.8).

Для построения счетчика с произвольным модулем М{, используется способ исключения лишних состояний. Счетчики с произвольным модулем используются в качестве делителей частоты, управляемых кодом в частоту, а также для формирования модулированных

Рис. 12.8. Временные диаграммы, поясняющие работу счетчика

импульсных последовательностей, которые используют для передачи сигналов через каналы связи в устройствах вывода сигналов.

Управляемый делитель частоты с исключением последних состояний счетчика содержит схему, которая формирует импульс принудительного сброса, если код на выходе N достиг определенного значения, заданного входным кодом К. Код счетчика в этом случае будет принимать значения от 0 до К, а период повторения импульсов сброса составит К + 1 период синхросигнала.

Исключение в качестве лишних некоторого числа первых состояний достигается путем загрузки начального кода К при переполнении. Код счетчика в этом случае изменяется от значения АТ до 2" - 1, в результате период повторения импульсов переполнения составит 2" - 1 - К периодов входной частоты.

Для построения счетчиков с заданным модулем в ПЛИС хорошо подходят библиотечные многофункциональные счетчики, однако более целесообразным является проектирование подобных устройств с описанием на HDL-языках.

Информация снимается с прямых и (или) инверсных выходов всех триггеров. В паузах между входными импульсами триггеры сохраняют свои состояния, т.е. счетчик запоминает число входных импульсов.

Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом. Остальные состояния нумеруются по числу поступивших входных импульсов. Когда число входных импульсов Nвх>Kсч происходит переполнение, после чего счетчик возвращается в нулевое состояние и цикл повторяется. Коэффициент счета, таким образом, характеризует число входных импульсов, необходимое для выполнения одного цикла и возвращения в исходное состояние. Число входных импульсов и состояние счетчика взаимно определены только для первого цикла.

После завершения каждого цикла на выходах последнего триггера возникают перепады напряжения. Это определяет второе назначение счетчиков: деление числа входных импульсов. Если входные сигналы периодичны и следуют с частотой F,,, то частота выходных сигналов равна Fвых=Fвх/Kсч. В этом случае коэффициент счета называется коэффициентом деления и обозначается как Кдел.

У счетчика в режиме деления используется выходной сигнал только последнего триггера, промежуточные состояния остальных триггеров во внимание не принимаются. Всякий счетчик может быть использован как делитель частоты. Поэтому подобное устройство часто называют счетчиком-делителем. Такие делители имеют целочисленный коэффициент деления. Однако элементная база современной микроэлектроники позволяет создавать делители и с дробными коэффициентами деления [5, 8].

Символом счетчиков на схемах служат буквы СТ (от англ. counter — счетчик), после символа проставляют число, характеризующее модуль счета (например, 2 или 10 — СТ2, СТ10).

Основными эксплуатационными показателями счетчика являются емкость и быстродействие. Емкость счетчика, численно равная коэффициенту счета, равна числу импульсов за один цикл.

Быстродействие счетчика определяется двумя параметрами: разрешающей способностью Тр„.„ и временем установки кода счетчика Туст. Под разрешающей способностью подразумевают минимальное время между двумя входными сигналами, в течение которого не возникают сбои в работе. Обратная величина Fмакс=l/Tpаз,cч, называется максимальной частотой счета. Время установки кода Туст равно времени между моментом поступления входного сигнала и переходом счетчика в новое устойчивое состояние. Эти параметры зависят от быстродействия триггеров и способа их соединения между собой.

Счетчики различаются числом и типами триггеров, способами связей между ними, кодом, организацией счета и другими показателями. Цифровые счетчики классифицируются по следующим параметрам [7, 8]:

О коэффициент счета — двоичные (бинарные); двоично-десятичные (декадные) или с другим основанием счета; с произвольным постоянным и переменным (программируемым) коэффициентом счета;

О направление счета — суммирующие, вычитающие и реверсивные;

О способ организации внутренних связей — с последовательным, параллельным или с комбинированным переносом, кольцевые.

Классификационные признаки независимы и могут встречаться в разных сочетаниях: например, суммирующие счетчики бывают как с последовательным, так и с параллельным переносом, они могут иметь двоичный, десятичный и иной коэффициенты счета.

Введением дополнительных логических связей — обратных и прямых — двоичные счетчики преобразуются в недвоичные. Наибольшее распространение получили десятичные (декадные) счетчики, работающие с К„=10 в двоично-десятичном коде (двоичный — по коду счета, десятичный — по числу состояний).

Десятичные счетчики организуются из четырехразрядных двоичных счетчиков. Избыточные шесть состояний исключаются введением дополнительных связей. Возможны два варианта построения схем: счет циклически идет от 0000 до 1001 и исходным состоянием служит 0110B=6D; счет происходит до 1111B=15D (В, D — обозначения двоичного и десятичного чисел). Первый вариант на практике применяется чаще.

В суммирующем счетчике каждый входной импульс увеличивает на единицу число, записанное в счетчик, при этом перенос информации из одного разряда в другой, более старший, имеет место, когда происходит смена состояния 1 на 0.

Вычитающий счетчик действует обратным образом: двоичное число, хранящееся в счетчике, с каждым поступающим импульсом уменьшается на единицу. Переполнение вычитающего счетчика происходит после достижения им нулевого состояния. Перенос из младшего разряда в старший здесь имеет место при смене состояния младшего разряда с 0 на 1.

Реверсивный счетчик может работать в качестве суммирующего и вычитающего. Эти счетчики имеют дополнительные входы для задания направления счета. Режим работы определяется управляющими сигналами на этих входах. В программе EWB такие счетчики представлены ИМС 74163 и 74169 (К155ИЕ18, ИЕ17).

Счетчики с последовательным переносом представляют собой цепочку триггеров, в которой импульсы, подлежащие счету, поступают на вход первого триггера, а сигнал переноса передается последовательно от одного разряда к другому.

Главное достоинство счетчиков с последовательным переносом — простота схемы. Увеличение разрядности осуществляется подключением дополнительных триггеров к выходу последнего триггера. Основной недостаток счетчиков с последовательным переносом — сравнительно низкое быстродействие, поскольку триггеры срабатывают последовательно, один за другим. Счетчики этого класса в библиотеке EWB не представлены.

Максимальная частота счета определяется режимом работы. Если считывание состояния счетчика должно происходить после каждого входного импульса, как это имеет место, например, при счете до заданного числа, то максимальная частота равна Fmax=l/[(m-l)Tэдп+Tсp], где т — число разрядов; Тэдп — задержка переключения одного триггера; Тер — время срабатывания внешнего элемента или считывающей схемы.

Счетчики с параллельным переносом состоят из синхронных триггеров. Счетные импульсы подаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующим только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, и задержка переключения всего счетчика равна задержке одного триггера. В таких счетчиках используются JK- и D-триггеры. В схемном отношении они сложнее счетчиков с последовательным переносом. Число разрядов у этих счетчиков обычно невелико (4...6), поскольку с повышением числа разрядов число внутренних логических связей быстро растет.

Счетчики с параллельным переносом применяются в быстродействующих устройствах. Они обладают более высокой помехоустойчивостью, так как в паузах между импульсами триггеры счетчика блокированы. К их недостаткам следует отнести меньшую нагрузочную способность отдельных разрядов из-за дополнительной нагрузки внутренними связями. Каскад, предшествующий счетчику, должен иметь достаточную мощность, чтобы управлять входами нескольких триггеров.

Счетчики с параллельным переносом (их чаще называют синхронными) в библиотеке EWB представлены счетчиками 74160, 74162, 74163 и 74169 (аналоги — К155ИЕ9, ИЕН, ИЕ18, ИЕ17 соответственно).

В счетчике с параллельно-последовательным переносом триггеры объединены в группы так, что отдельные группы образуют счетчики с параллельным переносом, а группы соединяются последовательно. В роли групп могут быть и готовые счетчики. Счетчики этого типа, как правило, многоразрядные. Общий коэффициент счета равен произведению коэффициентов счета всех групп. По быстродействию они занимают промежуточное положение.

Счетчики-делители, оформленные как самостоятельные изделия, имеются в составе многих серий микросхем. Номенклатуру счетчиков отличает большое разнообразие. Многие из них обладают универсальными свойствами и позволяют управлять коэффициентом и направлением счета, вводить до начала цикла исходное число, прекращать счет по команде, наращивать число разрядов и т.п. С помощью готовых счетчиков можно решить большинство практических задач, возникающих перед разработчиком аппаратуры.

В ряде случаев может возникнуть потребность в счетчиках с нетиповыми характеристиками. Они создаются из отдельных триггеров и логических элементов.

Проектирование счетчика сводится к определению числа триггеров и организации связей между ними и логическими элементами, а также вычислению разрешающей способности счетчика (максимальной частоты счета).

На первом шаге проектирования заданный коэффициент счета (деления) преобразуется в двоичный код. Число разрядов двоичного числа показывает, сколько триггеров должен иметь счетчик, а число единиц определяет число входов логического элемента. Входы элемента подключаются к прямым выходам Q тех триггеров, которые соответствуют единицам двоичного числа. Следует только учитывать, что первый, входной триггер отображает младший разряд числа. Выход логического элемента соединяется со входами установки нуля (входы R) всех триггеров, от которых сделаны отводы, а также тех, которые непосредственно за ними следуют.

Результаты проектирования применимы к триггерам разных видов логики, однако реальные схемы при этом могут различаться в деталях. Поскольку принудительная установка в нуль по R-входу у некоторых типов триггеров осуществляется сигналами логического нуля (ТТЛ, ДТЛ), у других — сигналами логической единицы (КМОП), в первом случае должен быть применен логический элемент И-НЕ, во втором — И. Кроме того, в суммирующем счетчике опрокидывание каждого последующего триггера должно происходить тогда, когда сигнал на выходе предыдущего триггера изменяется от 1 к 0, поэтому важен порядок соединения триггеров между собой. Если в счетчике применяются триггеры с прямым управлением (по фронту 0—>1), их входы присоединяются к инверсным выходам предыдущих. В случае триггеров с инверсным управлением входы подключают к прямым выходам. Добавив к исходной схеме несколько дополнительных элементов, можно расширить ее возможности — сделать счетчик с самоостановом (одноразового действия) или обеспечить в режиме деления кратковременный импульс на выходе последнего триггера.

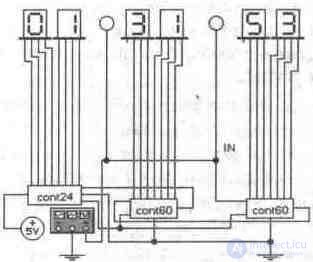

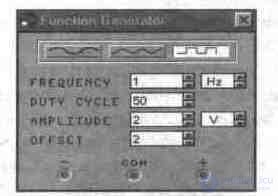

Порядок разработки устройств на базе счетчиков рассмотрим на примере цифровых часов, функциональная схема которых приведена на рис. 9.35. Часы содержат три пары индикаторов для отображения часов, минут, секунд и два одиночных индикатора-разделителя. Индикаторы управляются от подсхем cont24 и cont60 с питанием от источника +5V. В качестве задающего генератора используется функциональный генератор, режимы работы которого показаны на рис. 9.36.

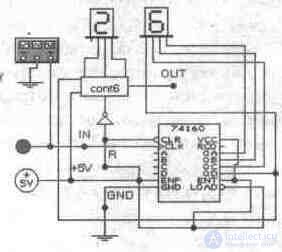

Следует отметить, что представленная на рис. 9.35 схема обладает крайне низким быстродействием, поэтому реализовать режим секундомера путем повышения частоты задающего генератора не удалось. Блок cont60 представляет собой счетчик с коэффициентом счета Ксч=60, его функциональная схема показана на рис. 9.37. Блок содержит подсхему-счетчик cont6 (Kcч=6) и двоично-десятичный счетчик 74160 (К155ИЕ9). Микросхема К155ИЕ9 (74160) — декадный двоично-десятичный счетчик . Он запускается положительным перепадом тактового импульса и имеет синхронную загрузку (предварительную установку каждого триггера по входам А, В, С, D). Несколько счетчиков ИЕ9 образуют синхронный многодекадный счетчик. Сброс всех триггеров — асинхронный по общему входу сброса R (CLR').

Рис. 9.35. Функциональная схема часов

Рис. 9.36. Панель функционального генератора в схеме часов

Рис. 9.37. Функциональная схема счетчика cont60

Счетчик содержит внутреннюю логику ускоренного переноса, и все триггеры получают перепад тактового импульса одновременно. Изменения выходных состояний триггеров совпадают по времени, поэтому в выходных импульсных последовательностях нет пиковых помех. Запускающий тактовый фронт импульса — положительный, причем для варианта этой микросхемы с переходами Шотки буферный элемент тактового входа имеет порог с гистерезисом 400 мВ, что уменьшает чувствительность к импульсным помехам, а также обеспечивает устойчивое переключение триггеров при медленно нарастающем перепаде тактового импульса.

Счетчик ИЕ9 — полностью программируемый, поскольку на каждом из его выходов можно установить требуемый логический уровень. Такая предварительная установка происходит синхронно с перепадом тактового импульса и не зависит от того, какой уровень присутствует на входах разрешения счета СЕР (ENP) и СЕТ (ENT). Напряжение низкого уровня, поступившее на вход параллельной загрузки РЕ (LOAD'), останавливает счет и разрешает подготовленным на входах DO...D3 (А, В, С, D) данным загрузиться в счетчик в момент прихода следующего положительного перепада тактового импульса (от низкого к высокому уровню или при переходе от 0 к 1).

Сброс счетчика ИЕ9 — асинхронный. Если на общий вход сброса R поступило напряжение низкого уровня, на выходах всех четырех триггеров устанавливаются низкие уровни независимо от сигналов на входах С (CLK), РЕ, СЕТ и СЕР. Внутренняя схема ускоренного переноса необходима для синхронизации многодекадной цепи счетчиков ИЕ9. Специально для синхронного каскадирования микросхема имеет два входа разрешения: СЕР (параллельный) и СЕТ (вспомогательный, с условным названием "трюковый"), а также выход ТС (RCD — окончание счета).

Счетчик считает тактовые импульсы, если на обоих его входах СЕР и СЕТ напряжение высокого уровня. Вход СЕТ последующего счетчика получает разрешение счета в виде напряжения высокого уровня от выхода ТС предыдущего счетчика. Длительность высоких уровней (сигнала логической 1) на выходе ТС примерно соответствует длительности высокого уровня на выходе QO предыдущего счетчика.

Для счетчиков ИЕ9 не допускаются перепады от высокого уровня к низкому на входах СЕР и СЕТ, если на тактовом входе присутствует напряжение низкого уровня. Нельзя подавать положительный перепад на вход РЕ, если на тактовом входе присутствует напряжение низкого уровня, а на входах СЕР и СЕТ — высокого (во время перепада или перед ним). Сигналы на входах СЕР и СЕТ можно изменять, если на тактовом входе С присутствует напряжение низкого уровня. Когда на входе РЕ появляется высокий уровень, а входы СЕ неактивны (т.е. на СЕР и СЕТ — низкий уровень), то вместе с последующим положительным перепадом тактового импульса на выходах QO...Q3 (QA, QB, QC, QD) появится код от входов DO...D3.

Подавая сигналы высокого уровня на входы СЕТ и СЕР при низком уровне сигнала на тактовом входе, получим на выходах наложение кодов загрузки и внутреннего счета. Если при низком уровне тактового сигнала на входы СЕТ, СЕР и РЕ поданы положительные перепады, нарастающие от низкого уровня к высокому, тактовый перепад изменит код на выходах QO...Q3 на последующий.

При входных сигналах высокого уровня счетчик К155ИЕ9 (74160) потребляет ток питания 94 мА, К555ИЕ9 (74 LS160A) — 32 мА; если все выходные сигналы имеют низкий уровень, то 101 и 32 мА соответственно. Максимальная частота счета 25 МГц. Время распространения сигнала от входа С до выхода ТС ("Счет закончен") составляет 35 и 27 нс, а время сброса (от входа R до выходов Q) 38 и 28 нс для обычного исполнения и варианта Шотки.

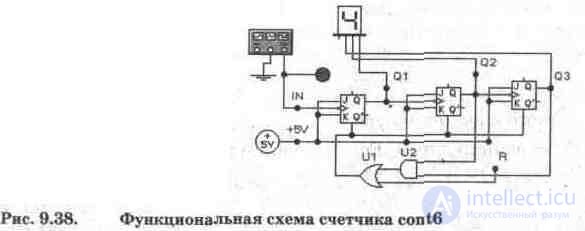

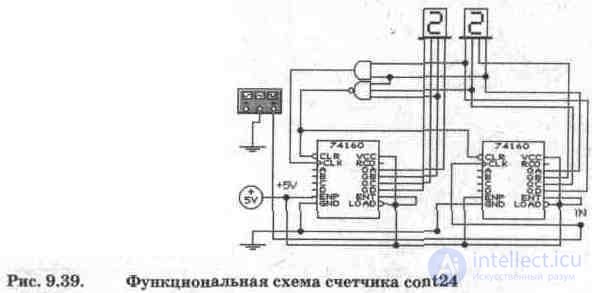

Схема счетчика cont6 показана на рис. 9.38. Счетчик выполнен на трех JK-триггерах в счетном режиме (на J- и К-входы поданы сигналы 1). Для обеспечения коэффициента счета Kсч=6 использована обратная связь на элементе И U2, который срабатывает при коде 110B=6D, при этом сигнал 1 с его выхода через элемент ИЛИ U1 поступает на R-входы триггеров, переводя их в нулевое состояние. Ко второму входу элемента U1 подключен вход R для подачи внешнего сигнала сброса. Поскольку для рассматриваемого счетчика и счетчика 74160 эти сигналы различны (для первого это 1, а для второго — 0), на входе R счетчика cont6 (рис. 9,37) включен инвертор. Схема счетчика часовых интервалов cont24 показана на рис. 9.39. Счетчик выполнен на двух ИМС 74160 и обеспечивает коэффициент Ксч=24.

Исследование, описанное в статье про счетчики цифровые, подчеркивает ее значимость в современном мире. Надеюсь, что теперь ты понял что такое счетчики цифровые, суммирующие счетчики , реверсивные счетчики, вычитающие счетчики, счетчик джонсона, асинхронный счетчик, синхронные счетчики и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ

Часть 1 Счетчики цифровые (суммирующие, реверсивные и вычитающие, Джонсона)

Часть 2 - Счетчики цифровые (суммирующие, реверсивные и вычитающие, Джонсона)

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ

Термины: Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ