Лекция

Game: Perform tasks and rest cool.1 people play!

Play gameСумматоры выполняют микрооперацию сложения слов. При сложении выполняется операция арифметического суммирования и дополнительные операции (учет знаков, порядок слагаемых и др.). Указанные операции выполняются в арифметико-логических устройствах (АЛУ), ядром которых являются сумматоры.

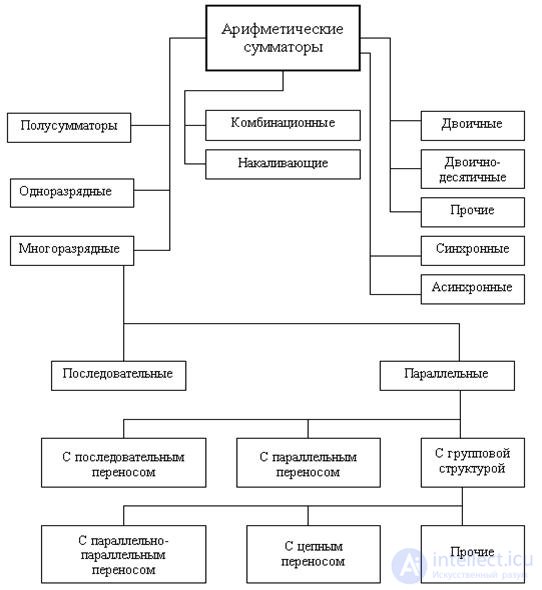

Классификация сумматоров показана на рисунке 4.1.

Рисунок 4.1 – Классификация арифметических сумматоров

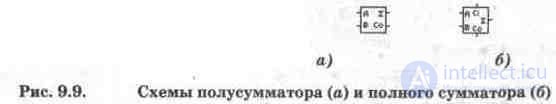

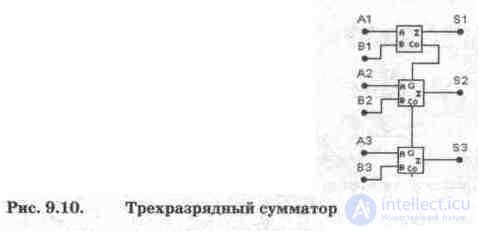

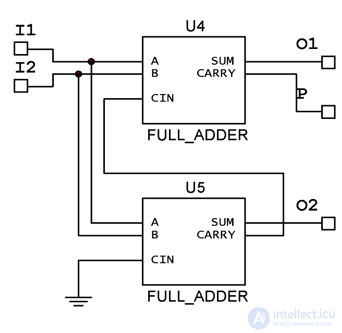

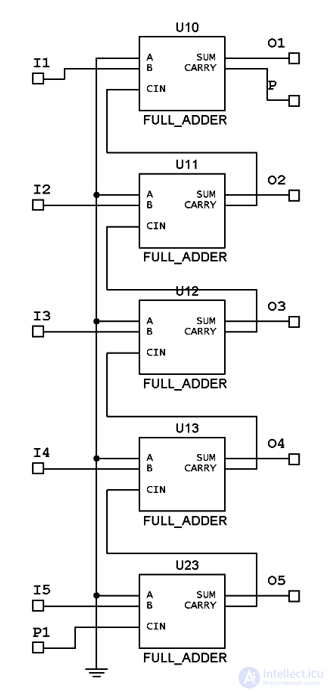

арифметические сумматоры являются составной частью так называемых арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти. В программе EWB арифметические сумматоры представлены в библиотеке Comb'I двумя базовыми устройствами, показанными на рис. 9.9: полусумматором и полным сумматором. Они имеют следующие назначения выводов: А, В — входы слагаемых, ? — результат суммирования. Со — выход переноса, Ci — вход переноса. Многоразрядный сумматор создается на базе одного полусумматора и га полных сумматоров. В качестве примера на рис. 9.10 приведена структура трехразрядного сумматора [20]. На входы Al, A2, A3 и Bl, B2, ВЗ подаются первое и второе слагаемые соответственно, а с выходов SI, S2, S3 снимается результат суммирования.

Game: Perform tasks and rest cool.1 people play!

Play game

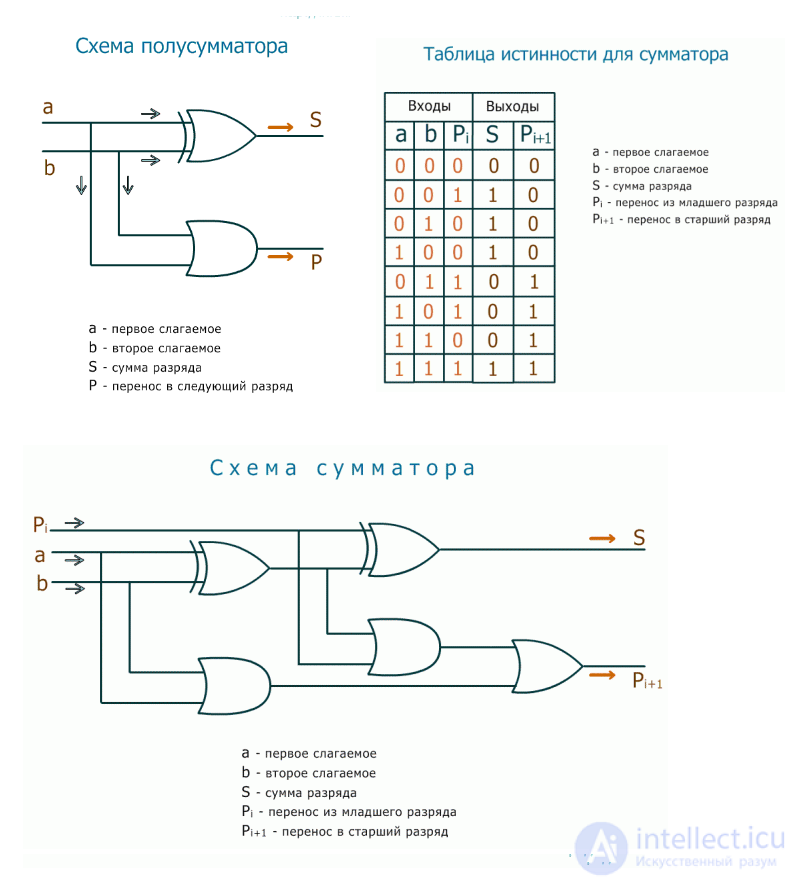

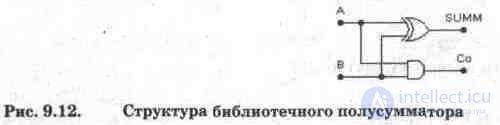

Для исследования внутренней структуры и логики функционирования сумматоров как нельзя лучше подходит логический преобразователь. После подключения полусумматора к преобразователю согласно рис. 9.11, а последовательно нажимаем кнопки  "pack.. в результате получаем таблицу истинности и булево выражение. Сравнивая полученные данные с результатами исследования базовых логических элементов в предыдущем разделе, приходим к выводу, что при подключении вывода (полусумматора к зажиму OUT преобразователя (как показано на рис. 9.11, а) он выполняет функции элемента Исключающее ИЛИ. Подключив клемму OUT преобразователя к выходу Со полусумматора и проделав аналогичные действия, приходим к выводу, что в таком включении полусумматор выполняет функции элемента И. Следовательно, эквивалентная схема полусумматора имеет вид, показанный на рис. 9.12.

"pack.. в результате получаем таблицу истинности и булево выражение. Сравнивая полученные данные с результатами исследования базовых логических элементов в предыдущем разделе, приходим к выводу, что при подключении вывода (полусумматора к зажиму OUT преобразователя (как показано на рис. 9.11, а) он выполняет функции элемента Исключающее ИЛИ. Подключив клемму OUT преобразователя к выходу Со полусумматора и проделав аналогичные действия, приходим к выводу, что в таком включении полусумматор выполняет функции элемента И. Следовательно, эквивалентная схема полусумматора имеет вид, показанный на рис. 9.12.

Game: Perform tasks and rest cool.1 people play!

Play game

module adder1(output sum, output c_out, input a, input b, input c_in);

assign sum = (a^b) ^ c_in;

assign c_out = ((a^b) & c_in) ^ (a&b);

endmodule

Просто важно понимать, что существуют разные методы описания, и нужно уметь ими всеми пользоваться.

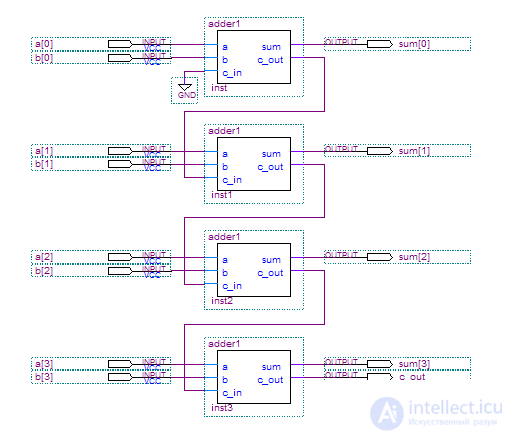

Теперь у нас есть однобитный сумматор и мы можем сделать, например, четырехбитный (с последовательным переносом)!

Вот так:

На Verilog это же будет выглядеть следующим образом:

module adder4(output [3:0]sum, output c_out, input [3:0]a, input [3:0]b );

wire c0, c1, c2;

adder1 my0_adder1( .sum (sum ) , .c_out (c0), .a (a ), .b (b ), .c_in (1’b0) );

adder1 my1_adder1( .sum (sum ) , .c_out (c1), .a (a ), .b (b ), .c_in (c0));

adder1 my2_adder1( .sum (sum ) , .c_out (c2), .a (a ), .b (b ), .c_in (c1));

adder1 my3_adder1( .sum (sum ) , .c_out (c_out), .a (a ), .b (b ), .c_in (c2) );

endmodule

Game: Perform tasks and rest cool.1 people play!

Play game

Цель – проектирование восьмиразрядного сумматора ± А ± В, который будет показывать сумму двух чисел на семисегментных индикаторах.

Кодирование отрицательных чисел

Для выполнения арифметических операций двоичные числа кодируются специальными машинными кодами: прямыми, дополнительными и обратными, позволяющими заменить операции вычитания операциями суммирования, что упрощает построение арифметическо-логических устройств.

Модифицированные коды

В отличие от обычных машинных кодов в модифицированных кодах под знак числа отводится два разряда: плюс изображается двумя нулями, а минус -двумя единицами. Это весьма удобно для выявления переполнения разрядной сетки, которое может получиться при сложении чисел с одинаковыми знаками.

Схема реализована в программе Electronics Workbench

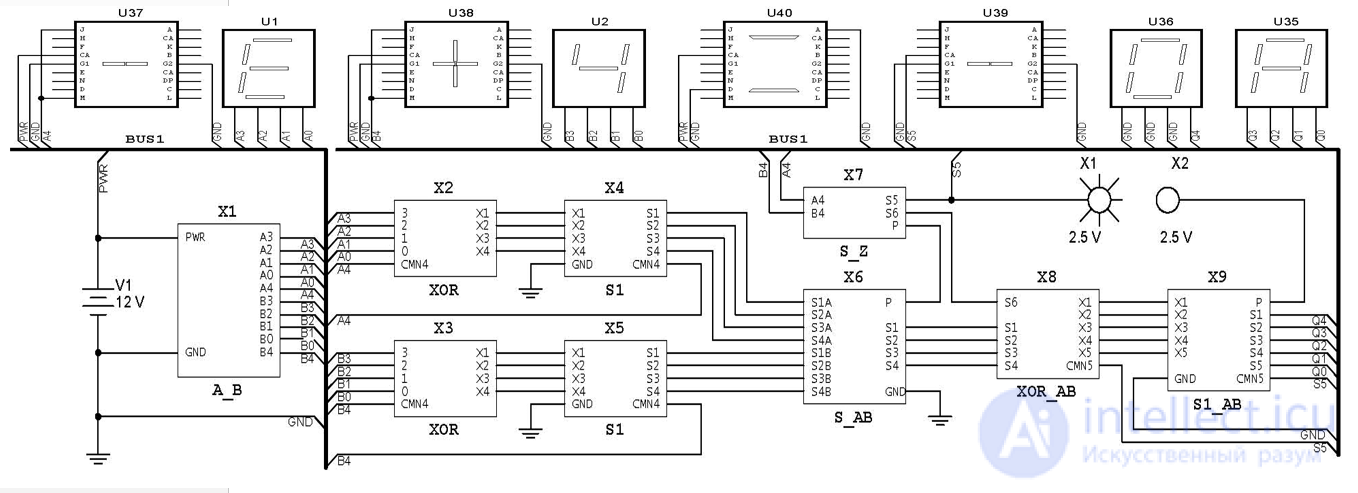

На рисунке 1 представлена разработанная схема восьмиразрядного сумматора:

Game: Perform tasks and rest cool.1 people play!

Play game

Данная схема содержит несколько блоков. Блоки представлены на рисунках ниже.

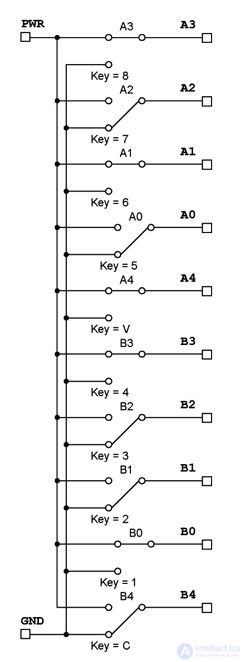

Схема блока KEY (ключа)

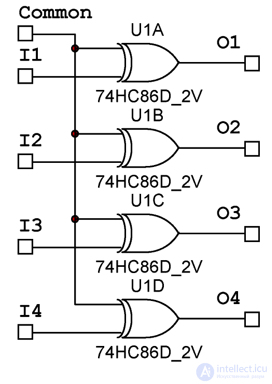

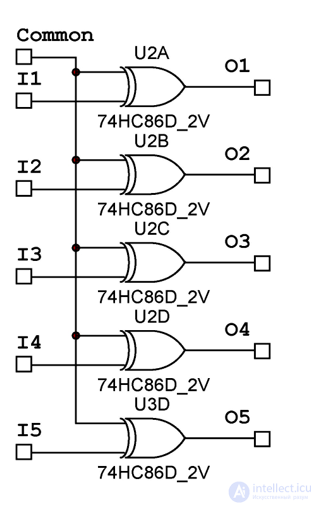

Схема блока XOR (одна из логических функций Булевой алгебры – сложение по модулю 2 )

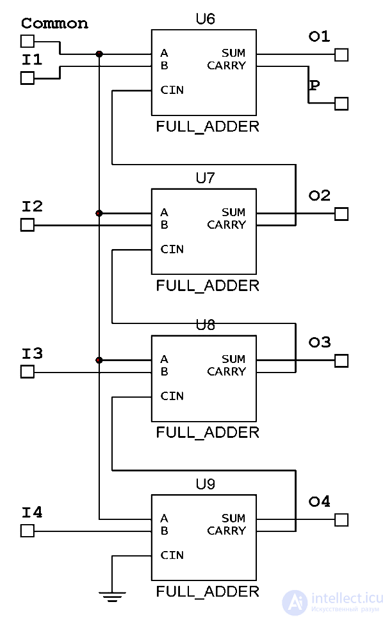

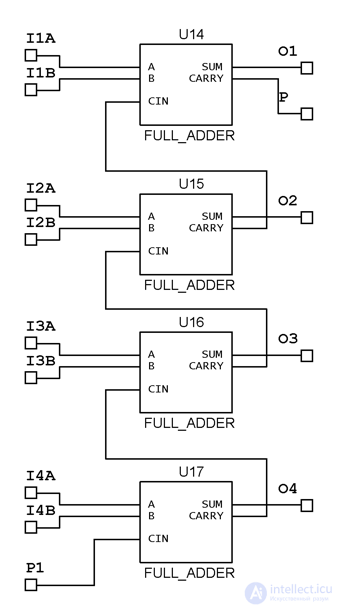

Схема блока S1

Схема блока S_AB

Схема блока S_Z

Схема блока XOR_AB

Схема блока S1_AB

Принцип работы:

пользователь с помощью размыкания или замыкания ключей формирует на выходе элемента A_B двоичные кода двух чисел, затем каждый двоичный код числа переводиться из прямого в обратный элементом XOR, элементы S1 переводят двоичный код числа из обратного в двоичный, затем два числа складываются с помощью элемента S_AB, а полученная сумма переводиться из дополнительного двоичного кода в прямой через элементы XOR_AB, S1_AB и результат выводиться на индикаторы. В порядке: сначала знак, десятки, потом единицы

Кнопки: 1, 2, 3, 4 - полубайт первого числа; 5, 6, 7, 8 - полубайт второго числа, С и V - знак первого и второго числа соответственно.

Например, чтобы сложить -4 и 6 нужно нажать: С, 3 и 6, 7. Сумматор сложит два числа и результат выведет в шестнадцатеричном виде -4+6=2(HEX).

Game: Perform tasks and rest cool.1 people play!

Play game

Цифровые арифметические сумматоры находят широкое применение в разнообразных электронных системах и устройствах, таких как:

Game: Perform tasks and rest cool.1 people play!

Play gameПроцессоры и микроконтроллеры:

Калькуляторы:

Системы обработки данных:

Шифраторы и дешифраторы:

Графические процессоры (GPU):

Цифровые фильтры:

Системы автоматического управления:

Математические модели и симуляции:

Их важность заключается в том, что они могут быстро и эффективно выполнять арифметические операции, что критично для большинства цифровых систем, включая вычислительные устройства, системы связи и управления.

1. Какое устройство используется для сложения двух двоичных чисел?

2. Какое устройство выполняет арифметические и логические операции в компьютере?

Game: Perform tasks and rest cool.1 people play!

Play game3. Что означает термин "полусумматор"?

4. Какое из следующих устройств выполняет сложение с переносом?

5. Какой тип сумматора может складывать два двоичных числа без учета переноса?

6. Что такое полный сумматор?

7. Какой из перечисленных компонентов является частью ALU?

8. Что обозначает термин "арифметическое переполнение"?

Game: Perform tasks and rest cool.1 people play!

Play game9. Как называется ошибка, когда результат сложения выходит за пределы диапазона?

10. Какое устройство используется для преобразования двоичных чисел в другие формы?

11. Какую задачу решает цифровой сумматор?

Game: Perform tasks and rest cool.1 people play!

Play game12. Что такое мультиплексор?

13. Какой тип схемы используется для выполнения сложения с переносом?

14. Что представляет собой логическая схема, которая выполняет операцию сложения двух двоичных чисел?

15. В каком устройстве реализованы операции сложения и вычитания?

16. Как называется схема, которая суммирует три и более двоичных числа?

17. Что выполняет операцию сложения двух 1-битных чисел и выдает результат и перенос?

Game: Perform tasks and rest cool.1 people play!

Play game18. Какой компонент выполняет сложение без учета переноса?

19. Как называется устройство, которое выбирает один из нескольких входов для передачи на выход?

20. Что означает термин "одноразрядный сумматор"?

Game: Perform tasks and rest cool.1 people play!

Play gameЭти тесты охватывают основные понятия и устройства, связанные с цифровыми сумматорами и логическими схемами.

1. Чем отличается полусумматор от полного сумматора?

2. Выясните внутреннюю структуру полного сумматора, пользуясь схемой его подключения к логическому преобразователю на рис. 9.11, б и принимая во внимание методику решения аналогичной задачи для полусумматора.

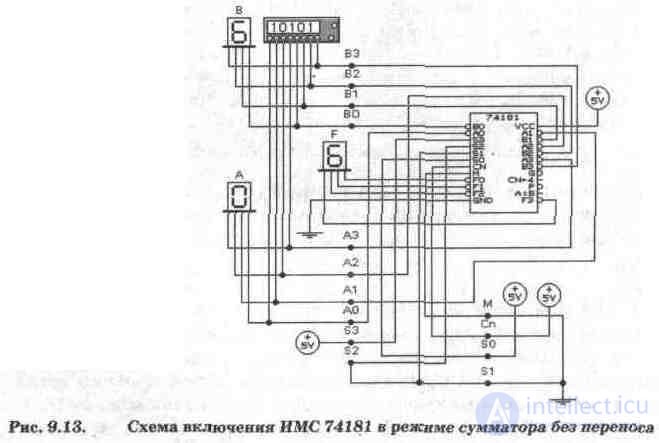

3. Используя опыт работы со схемой на рис. 9.13, подключите ко входам трехразрядного сумматора на рис. 9.10 генератор слова, а к выходам — алфавитно-циф-ровой индикатор с дешифратором и проверьте правильность его функционирования.

4. Проверьте работу ИМС 74181 в режиме сумматора с переносом (на вход Сп подайте сигнал логического нуля), в

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Комментарии

Оставить комментарий

Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ

Термины: Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ