Лекция

Сразу хочу сказать, что здесь никакой воды про триггер, и только нужная информация. Для того чтобы лучше понимать что такое триггер, асинхронный rs-триггер, t-триггеры, синхронный rs триггер, d-триггер, jk-триггер, sr-триггер, flip-flop , настоятельно рекомендую прочитать все из категории Электроника, Микроэлектроника , Элементная база.

триггер (триггерная система, flip-flop ) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознается по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

При включении питания триггер непредсказуемо принимает (с равной или неравной вероятностью) одно из двух состояний. Это приводит к необходимости выполнять первоначальную установку триггера в требуемое исходное состояние, то есть подавать сигнал сброса на асинхронные входы триггеров, счетчиков, регистров, и т. д. (например, с помощью RC-цепочки), а также учитывать, что ячейки ОЗУ, построенного на триггерах (память статического типа), содержат после включения произвольную информацию.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно биполярные и полевые транзисторы), в прошлом — электромагнитные реле, электронные лампы. С появлением технологии производства микросхем малой и средней степени интеграции был освоен выпуск обширной номенклатуры триггеров в интегральном исполнении. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС). Используются, в основном, в вычислительной технике для организации компонентов вычислительных систем: регистров, счетчиков, процессоров, ОЗУ.

Триггер - электронное устройство, которое может сохранять одно из двух возможных состояний.

Триггер — это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одного бита информации, то есть имеет состояния логического 0 или логической 1.

Триггер — это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одного бита информации, то есть имеет состояния логического 0 или логической 1.

Триггер (бистабильный мультивибратор — это цифровой автомат, имеющий несколько входов и 2 выхода.

Триггер — это электронная ячейка памяти, функционирующая подобно миниатюрному выключателю, способному длительно сохранять одно из двух состояний (0 или 1) и переключаться между ними только при поступлении специального управляющего сигнала. В отличие от обычных переключателей, триггер запоминает свое состояние и стабильно удерживает его даже после исчезновения внешних воздействий, выступая фундаментальным элементом для построения логических схем, счетчиков, регистров и памяти цифровых устройств.

Триггер — это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется.

Триггерами называют такие логические устройства, выходные сигналы которых определяются не только сигналами на входах, но и предысторией их работы, то есть состоянием элементов памяти.

Триггер — один из базовых (основных) элементов цифровой техники. Некоторые исследователи включают триггер в 100 великих изобретений.

Триггер не является логическим элементом первого уровня, а сам состоит из логических элементов первого уровня — инверторов или логических вентилей. По отношению к логическим элементам первого уровня триггер является логическим устройством второго уровня.

Триггер — элементарная ячейка оперативной памяти.

Триггер — простейшее устройство, выполняющее логическую функцию с обратной связью, то есть простейшее устройство кибернетики.

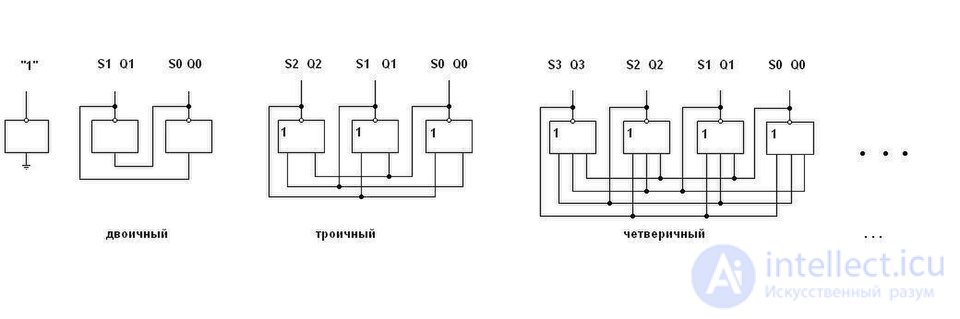

N-ичный триггер — устройство (элементарная переключаемая ячейка памяти, переключатель с N устойчивыми положениями), которое имеет N устойчивых состояний и возможность переключения из любого состояния в любое другое состояние.

Триггер — это логическое устройство с двумя устойчивыми состояниями 0 и 1, имеющие несколько входов и два выхода, один прямой, а другой инверсный.

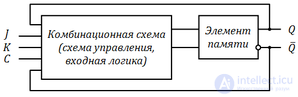

Все разновидности триггеров представляют собой конечный автомат, включающий собственно элемент памяти (ЭП) и комбинационную схему (КС), которая может называться схемой управления или входной логикой триггера (рисунок 7).

Рисунок 7. Обобщенная структура триггера

В графе триггера каждая вершина графа соединена со всеми другими вершинами, при этом переходы от вершины к вершине возможны в обе стороны (двухсторонние). Граф двоичного триггера — две точки соединенные отрезком прямой линии, троичного триггера — треугольник, четверичного триггера — квадрат с диагоналями, пятеричного триггера — пятиугольник с пентаграммой и т. д. При N=1 граф триггера вырождается в одну точку, в математике ему соответствует унарная единица или унарный ноль, а в электронике — монтажная «1» или монтажный «0», то есть простейшее ПЗУ. Устойчивые состояния имеют на графе триггера дополнительную петлю, которая обозначает, что при снятии управляющих сигналов триггер остается в установленном состоянии.

Состояние триггера определяется сигналами на прямом и инверсном выходах. При положительном представлении (позитивная логика) высокий уровень напряжения на прямом выходе отображает значение логической 1 (состояние = 1), а низкий уровень — значение логического 0 (состояние = 0). При отрицательном представлении (негативная логика) высокому уровню (напряжению) соответствует логическое значение 0, а низкому уровню (напряжению) соответствует логическое значение 1.

Изменение состояния триггера (его переключение или запись) обеспечивается внешними сигналами и сигналами обратной связи, поступающими с выходов триггера на входы схемы управления (комбинационной схемы или входной логики). Обычно внешние сигналы, как и входы триггера, обозначают латинскими буквами R, S, T, C, D, V и др.

В простейших схемах триггеров отдельная схема управления (КС) может отсутствовать. Поскольку функциональные свойства триггеров определяются их входной логикой, то названия основных входов переносятся на название триггера.

Входы триггеров разделяются на информационные (R, S, T и др.) и управляющие (С, V). Информационные входы предназначены для приема сигналов запоминаемой информации. Названия входных сигналов отождествляют с названиями входов триггера. Управляющие входы служат для управления записью информации. В триггерах может быть два вида управляющих сигналов:

На V-входы триггера поступают сигналы, которые разрешают (V=1) или запрещают (V=0) запись информации. В синхронных триггерах с V-входом запись информации возможна при совпадении сигналов на управляющих С и V-входах.

Работа триггеров описывается с помощью таблицы переключений, являющейся аналогом таблицы истинности для комбинационной логики. Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) либо (t-1) или после подачи сигнала (t+1) или (t). В триггерах с парафазным (двухфазным) выходом имеется второй (инверсный) выход, который обозначают как Q, /Q или Q'.

Кроме табличного определения работы триггера существует формальное задание функции триггера в формулах секвенциальной логики. Например, функцию RS-триггера в секвенциальной логике представляет формула:

Аналитическая запись sr-триггер а выглядит так:

Все разновидности триггеров представляют собой конечный автомат, включающий собственно элемент памяти (ЭП) и комбинационную схему (КС), которая может называться схемой управления или входной логикой триггера (рисунок ).

Входы триггера подразделяются на:

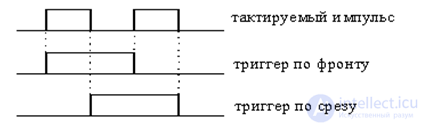

Триггеры запускаются по фронту или по срезу

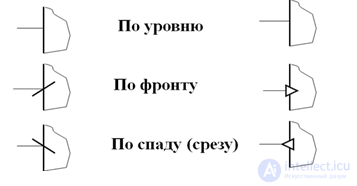

Обозначения воздействия исполнительного импульса

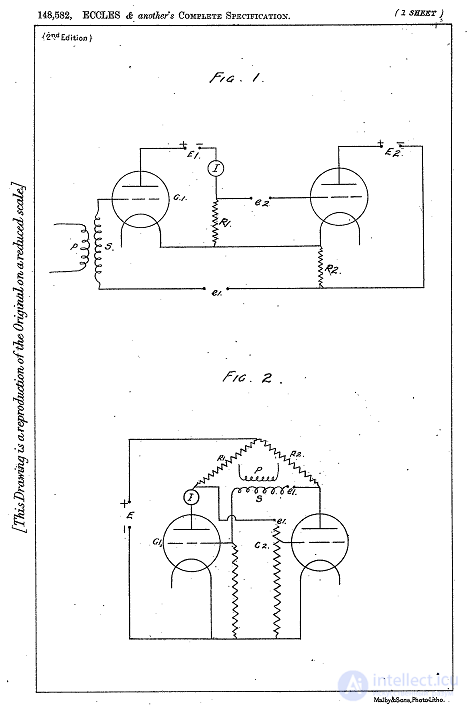

Рис.2 Схемы из патента Икклза и Джордана 1918 г., один (рис.1) нарисован как два инвертирующих каскада усилителя с положительной обратной связью, другой (рис.2) как симметричная перекрестносвязанная пара.

Рисунок 3. Временные диаграммы установки и сброса динамического триггера

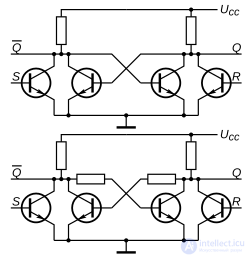

Рисунок 4. Симметричные триггеры на биполярных транзисторах: сверху — с непосредственной связью между каскадами; снизу — с резистивной связью

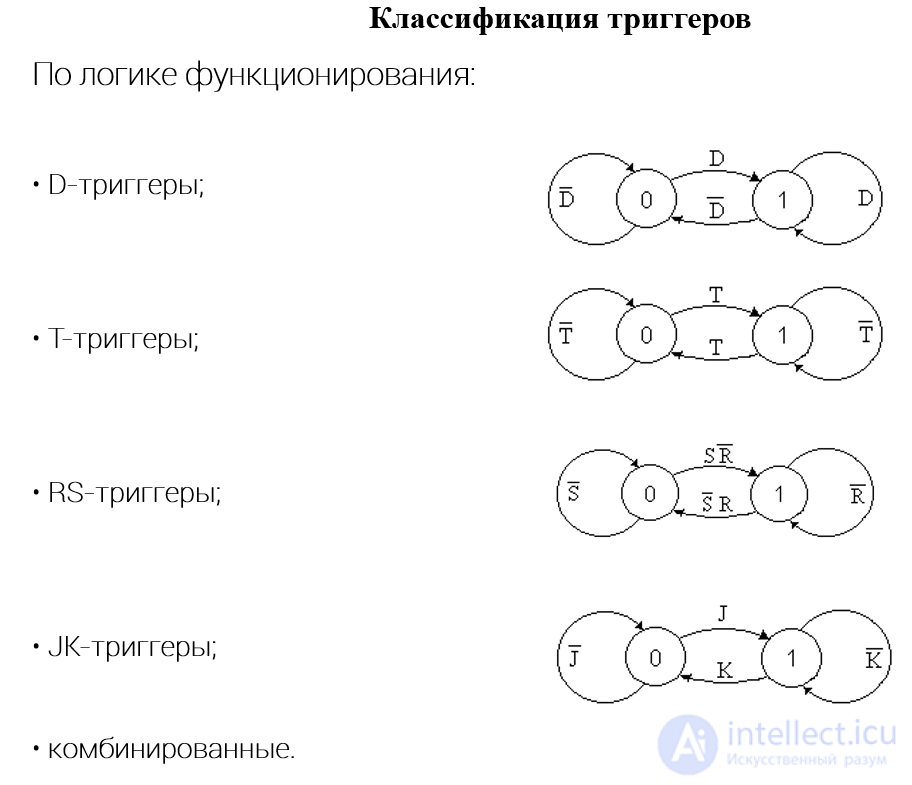

Рисунок 5. Функциональная классификация триггеров

Триггеры подразделяются на две большие группы — динамические и статические. Названы они так по способу представления выходной информации.

Динамический триггер представляет собой управляемый генератор, одно из состояний которого (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определенной частоты, а другое (нулевое) — отсутствием выходных импульсов. Смена состояний производится внешними импульсами (рисунок 3).

К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким — близким к напряжению питания и низким — около нуля. Статические триггеры по способу представления выходной информации часто называют потенциальными.

Статические (потенциальные) триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы — симметричные и несимметричные триггеры. Оба класса реализуются на двухкаскадном усилителе из двух инверторов с положительной обратной связью, а названием своим они обязаны способам организации внутренних электрических связей между элементами схемы.

Симметричные триггеры отличает симметрия схемы и по структуре, и по параметрам элементов обоих плеч. Для несимметричных триггеров характерна неидентичность параметров элементов отдельных каскадов, а также и связей между ними.

Симметричные статические триггеры составляют основную массу триггеров, используемых в современной радиоэлектронной аппаратуре. Схемы симметричных триггеров в простейшей реализации (2х2ИЛИ-НЕ) показаны на рисунке 4.

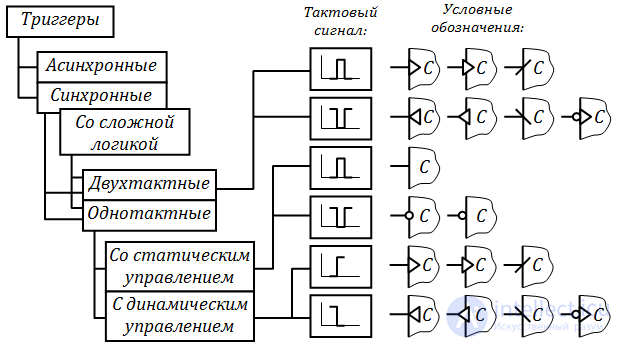

Основной и наиболее общий классификационный признак — функциональный — позволяет систематизировать статические симметричные триггеры по способу организации логических связей между входами и выходами триггера в определенные дискретные моменты времени до и после появления входных сигналов. По этой классификации триггеры характеризуются числом логических входов и их функциональным назначением (рисунок 5).

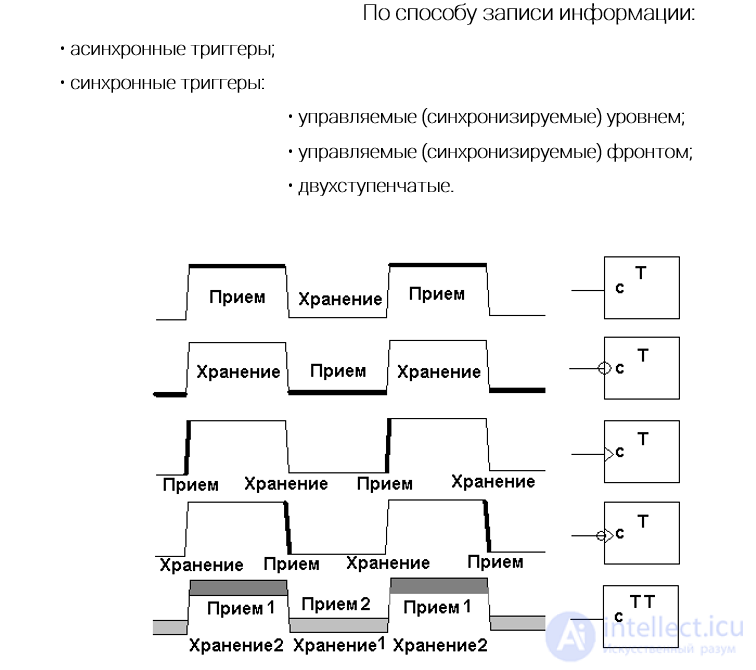

Вторая классификационная схема, независимая от функциональной, характеризует триггеры по способу ввода информации и оценивает их по времени обновления выходной информации относительно момента смены информации на входах (рисунок 6).

Каждая из систем классификации характеризует триггеры по разным показателям и поэтому дополняет одна другую. К примеру, триггеры RS-типа могут быть в синхронном и асинхронном исполнении.

Асинхронный триггер изменяет свое состояние непосредственно в момент изменения соответствующего информационного сигнала или сигналов, с некоторой задержкой равной сумме задержек на элементах, составляющих данный триггер.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. Об этом говорит сайт https://intellect.icu . clock). Этот вход также обозначают термином «такт». Такие информационные сигналы называют синхронными. Синхронные триггеры в свою очередь подразделяют на триггеры со статическим и с динамическим управлением по входу синхронизации С.

Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Также встречается название «триггер управляемый фронтом».

Одноступенчатые триггеры (latch, защелки) состоят из одной ступени представляющей собой элемент памяти и схему управления, бывают, как правило, со статическим управлением. Одноступенчатые триггеры с динамическим управлением применяются в первой ступени двухступенчатых триггеров с динамическим управлением. Одноступенчатый триггер на УГО(Условное графическое обозначение) обозначают одной буквой Т.

Двухступенчатые триггеры (flip-flop, «шлепающие») делятся на триггеры со статическим управлением и триггеры с динамическим управлением. При одном уровне сигнала на входе С информация, в соответствии с логикой работы триггера, записывается в первую ступень (вторая ступень заблокирована для записи). При другом уровне этого сигнала происходит копирование состояния первой ступени во вторую (первая ступень заблокирована для записи), выходной сигнал появляется в этот момент времени с задержкой равной задержке срабатывания ступени. Обычно двухступенчатые триггеры применяются в схемах, где логические функции входов триггера зависят от его выходов, во избежание временны́х гонок. Двухступенчатые триггеры в условных графических обозначениях (УГО) обозначают двумя буквами ТТ.

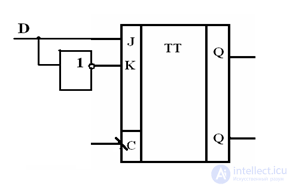

Двухступенчатый синхронный d-триггер с асинхронными сбросом и установкой

Триггеры со сложной логикой бывают также одно- и двухступенчатые. В этих триггерах наряду с синхронными сигналами присутствуют и асинхронные. Такой триггер изображен на рисунке справа, верхний (S) и нижний (R) входные сигналы являются асинхронными.

Триггерные схемы классифицируют также по следующим признакам:

Рисунок Классификация триггеров по типу синхронизации

Триггеры являются основными элементами цифровых систем и используются для хранения и передачи информации. Существует несколько различных типов триггеров, включая асинхронные RS-триггеры, t-триггеры , синхронные RS-триггеры, D-триггеры и jk-триггер ы. Давайте рассмотрим каждый из них подробнее.

S - set – установка в «1» Обозначение

R – reset – сброс в «0»

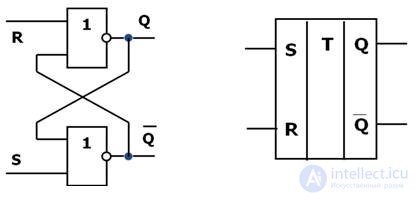

RS – триггер асинхронный, т.е. переход из одного состояния в другое не связано с тактовыми сигналами.

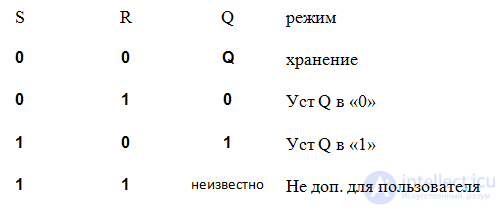

Таблица истинности RS-триггера

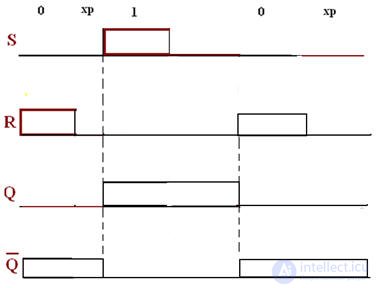

Временные диаграммы асинхронного RS-триггера

Асинхронный RS-триггер является самым простым типом триггера и состоит из двух входов: R (Reset) и S (Set). Он позволяет установить или сбросить свое состояние в зависимости от значений этих входов. Когда вход R устанавливается в 0 (или логическую "ложь"), а вход S устанавливается в 1 (или логическую "истину"), триггер устанавливается в состояние 1. Когда вход S устанавливается в 0, а вход R устанавливается в 1, триггер сбрасывается в состояние 0. Если оба входа R и S установлены в 1, то состояние триггера неопределено.

Обозначение

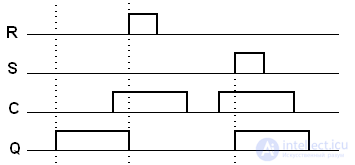

Предварительно на Q=«1», изменение на «0» возможно, когда наR и C «1», если надо на Q=1, то S=1 и C=1 и т.д.

Временные диаграммы

Синхронный RS-триггер также имеет входы R и S, но кроме того, он имеет вход синхронизации CLK. Изменение состояния триггера происходит только при поступлении сигнала синхронизации. Когда сигнал CLK равен 1, входы R и S проверяются. Если R=0 и S=1, то триггер устанавливается в 1. Если R=1 и S=0, то триггер сбрасывается в 0. Если оба входа R и S равны 0 или оба равны 1, то состояние триггера не изменяется.

. Такое название он получил за свои два входа: S (set) - записывает в триггер единицу, а R (reset) - записывает ноль. А еще у него есть аж целых два выхода: прямой (Q) и инверсный (!Q). На прямой выход выводится значение ячейки, а на инверсный, соответственно названию, - инвертированное значение. Как по мне, хватило бы и одного выхода. Понятия не имею, зачем так сделано, может быть, дань традициям. Тем не менее, вот так можно собрать триггер из парочки элементов ИЛИ и парочки НЕ:

Эта конструкция примечательна тем, что в ней есть обратная связь. Значение с инвертированного выхода подается на вход в верхний эелемент ИЛИ и таким образом держит весь триггер в нулевом состоянии. Если теперь попробовать сбросить значение и подавать единицу на вход Reset, то ничего не поменяется. Но вот если подать единицу на вход Set, то триггер переключится в другое состояние.

Пожалуй, лучше посмотреть, как элементы будут переключаться:

Итого получается, что, когда на вход ничего не подается, то триггер сохраняет свое состояние. А еще его состояние можно устанавливать в единицу или сбрасывать в ноль. Казалось бы, и все, но остался еще один случай, доселе не рассмотренный, - подать единицу на оба входа! В таком случае оба элемента ИЛИ будут выдавать единицу. А оба элемента НЕ будут эту единицу конвертировать в ноль. И значит, на выходе и прямом, и инверсном будет тоже ноль. Вот, полюбуйтесь:

Выходит, что в ячейке сейчас записан ноль. Но и инвертированное значение тоже ноль. А хуже всего то, что если одновременно на оба входа теперь подать ноль, то непонятно, в каком состоянии будет после этого триггер. Поэтому такую ситуацию называют “Запрещенным состоянием”, и делать так нельзя. Это, конечно, не то же самое, что и короткое замыкание. То есть, ничего страшного, просто нельзя. Примерно как делить на ноль. Тоже ведь нельзя, но если уж не удержался и разделил, то ничего страшного. А еще триггер принимает неопределенное состояние при включении, в случае, когда на всю плату подается питание. Так что после включения надо обязательно его сбросить перед использованием.

Приведенный выше триггер является асинхронным. Логично предположить, что бывают еще и синхронные триггеры. В электронике (да и вообще много где) очень полезно, когда компоненты работают согласованно. Для схожих вещей, например, в оркестре ставят дирижера. Он показывает начало тактов и таким образом синхронизирует всех музыкантов. Электрический аналог дирижера - это тактовый генератор. Он вырабатывает ритм для синхронизирования электронных компонентов определенной частоты. Именно эту частоту можно увидеть в характеристиках процессора или материнской платы. Так вот синхронный триггер срабатывает под действием синхронизирующего сигнала. Для этих целей у него есть еще один дополнительный вход C (от слова clock). Ниже располагается пример синхронного триггера, в котором записан ноль (слева). Потом подается сигнал на S для установки единицы, но ничего не происходит (посередине), пока не придет синхроимпульс. И только с приходом синхронизирующего сигнала ячейка переключается в единицу (справа).

Уже неплохо, теперь, пока на тактовой линии держится ноль, триггер вообще никак не реагирует на SR входы. Зато вот когда от тактового генератора приходит единица, то ячейка ведет себя, как асинхронная. Например, по какой-то причине сразу после установки единицы в триггере на вход R тоже приходит единица. И вот тут все зависит от того, успеет ли тактовый генератор переключиться в ноль или нет. На иллюстрации ниже в первом случае генератор не успевает, и сигнал сброса приходит раньше. А во втором случае, сначала переключается тактовый сигнал, а уже потом приходит сброс.

Сверху получилось запрещенное состояние. Правда Logisim не будет показывать состояние E, а просто упадет с ошибкой, эту ситуацию я руками нарисовал для наглядности.

Есть случаи, когда такое срабатывание не годится. Тогда триггер должен менять свое состояние мгновенно во время перепада напряжения тактового сигнала. Для таких случаев собирают двухступенчатый триггер:

Тут просто две SR ячейки, стоящие друг за другом. Первая ячейка управляется от внешних входов, а вторая ячейка - от первой. Для этого прямой выход (Q) с первого триггера соединяем со входом S второго. Чтобы единица, записанная в первый триггер, также записывалась и во второй. Хитрость тут в том, что на первый триггер подается тактовый сигнал, как есть, а на второй - инвертированный. Таким образом, пока тактовый сигнал - единица, то, меняя S и R входы, можно менять состояние первого триггера. Но при этом второй триггер остается неизменным, и значение на выходе - тоже. А вот как только тактовый сигнал меняется, то тогда первый триггер остается, как есть, ведь для него теперь тактовый сигнал является нулем. Второй же триггер теперь включен и готов к изменениям, вот только на вход ему приходят данные от первого, который не изменяется. В общем, этот двухступенчатый триггер теперь меняет свое состояние только в случае, когда тактовый сигнал переходит из 1 в 0. Если надо, чтобы он переключался на переход из 0 в 1, то можно добавить еще один инвертор на вход C:

Не стоит забывать, что при подаче питания, то есть при первом включении, сложно предсказать, что же будет записано в триггере. И было бы неплохо иметь возможность просто и без хлопот сбросить значение триггера в 1 или 0 по желанию. Для таких вещей можно вывести еще два дополнительных входа, асинхронных. Теперь в триггер можно записать 0 или 1, не дожидаясь синхроимпульса. У следующей версии триггера, помимо всего прочего, теперь есть еще и асинхронные входы. И, как можно увидеть, - это просто S и R входы из асинхронной версии SR триггера.

Тут я заменил элементы ИЛИ с двумя входами, на трехвходовые. Они работают точно так же: выдают единицу, если хотя бы на один вход приходит единица.

Но и на этом не обязательно останавливаться. Можно добавить еще один вход - Enable (включить). Из названия очевидно, что, когда на вход “включить” подается сигнал, то триггер включается и начинает реагировать на синхронные входы. Кстати, при этом значение элемента подается на выходы всегда, вне зависимости от того, в каком состоянии Enable. То есть, если сначала в триггер записать единицу, а потом его выключить (подать в Enable ноль), то он все равно будет выдавать единицу на выходе. Чтобы подвести сигнал включения, к каждому элементу И я добавил еще один вход:

Ну вот и все. Вот так вот можно собрать SR триггер из простейших логических элементов. В Logisim для обозначения этого триггера есть специальный элемент:

Я к нему подвел входы и выходы для наглядности. Дело в том, что поначалу я не понимал, зачем внизу там подписано “1en0”. Оказалось, это просто 3 разных входа. Вдобавок, в середине элемента отображается его внутреннее состояние. Это очень удобно, чтобы быстро понять, что же в нем записано:

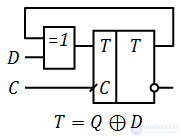

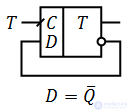

D-триггер – (триггер задержки данных delay ) - синхронный триггер, выходное состояние которого совпадает с сигналом на его информационном входе (D-входе), которое тот имел на предыдущем такте импульсов синхронизации

Условное обозначение и Таблица истинности срабатывания триггера по фронту

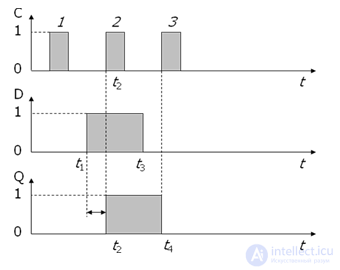

Временные диаграммы

D-триггер задерживает на 1 такт информацию, существующую на входе D.

На D – триггерах могут быть построены регистры, чтобы заполнить 8-ми разрядное слово надо 8 D-триггеров.

Информация в D-триггерах хранится до тех пор, пока не придет разрешение на смену информации и тогда запишется другое число

D-триггер имеет один вход D (Data) и вход синхронизации CLK. На каждом положительном фронте сигнала синхронизации D-триггер копирует значение на входе D и сохраняет его. Таким образом, он запоминает один бит информации. D-триггер широко применяется в цифровых системах для регистрации данных.

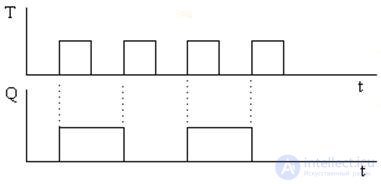

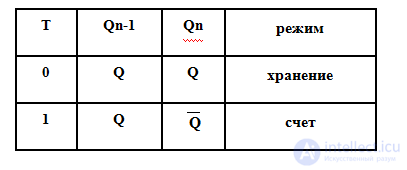

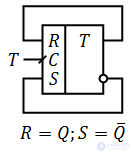

Счетный триггер (Т-триггер) изменяет свое состояние всякий раз при наличии активного уровня сигнала на его единственном информационном входе Т.

Обозначение

Т-триггер – делитель частоты на 2.

Временные диаграммы

Таблица истинности

T-триггер использует один вход T (Toggle). Он изменяет свое состояние на противоположное при поступлении сигнала на вход T, когда вход синхронизации (обычно обозначается как CLK) имеет положительный фронт. Если текущее состояние триггера равно 0 и поступает сигнал на вход T, то состояние изменяется на 1. Если текущее состояние равно 1, то состояние изменяется на 0. Т-триггер часто используется для создания счетчиков и делителей частоты.

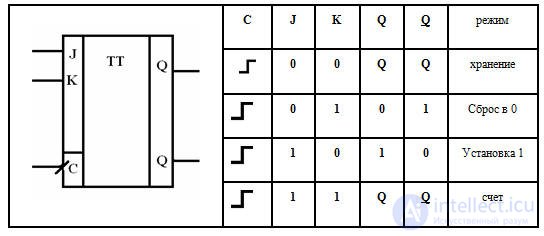

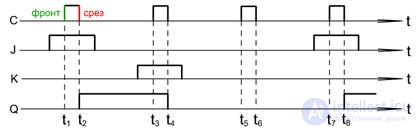

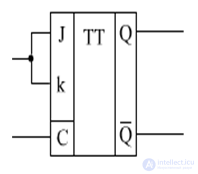

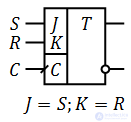

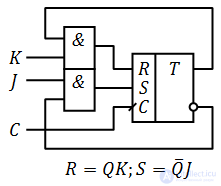

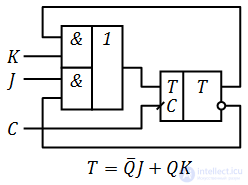

Обозначение Таблица истинности

Временные диаграммы

Если соединить J и k, то получаем Т-триггер. Т-триггер, при С=1

D-триггер на JK-триггере

JK-триггер имеет два входа J и K, а также вход синхронизации CLK. Он предоставляет больше функциональности, чем другие триггеры. Когда сигнал CLK равен 1, входы J и K проверяются. Если J=0 и K=1, триггер сбрасывается в 0. Если J=1 и K=0, триггер устанавливается в 1. Если J=1 и K=1, то состояние триггера инвертируется. Если J=0 и K=0, то состояние триггера не изменяется.

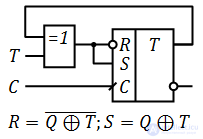

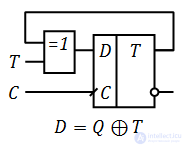

Так как любой из четырех рассматриваемых типов триггеров (RS, D, JK, T) является универсальным, на его базе с помощью дополнительных логических элементов можно реализовать триггер любого другого типа. В таблице показаны примеры такой реализации.

| Целевой тип |

RS-триггер | D-триггер | JK-триггер | ТC-триггер |

|---|---|---|---|---|

| RS |  |

|

|

|

| D |  |

|

|

|

| JK |  |

|

|

|

| ТC |  |

|

|

|

| Т |  |

|

|

Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала(ов), с некоторой задержкой равной сумме задержек на элементах, составляющих данный триггер.

D-триггер с динамическим тактированием

Синхронные триггеры с динамическим тактированием изменяют свое состояние только в момент определенного перехода тактового сигнала (либо 0→1, либо 1→0, то есть по переднему или заднему фронту тактового импульса). При неизменном уровне сигнала на тактовом входе никакие изменения на информационных входах не отражаются на состоянии триггера.

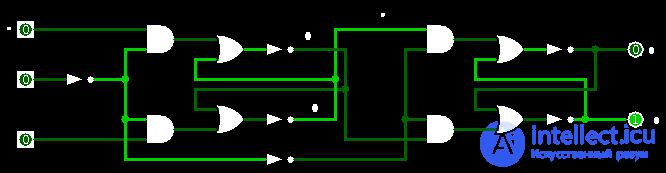

На рисунке показана схема D-триггера с тактированием по переднему фронту тактового сигнала.

Триггер состоит из трех асинхронных RS-триггеров на элементах И-НЕ. Один из триггеров основной (DD5, DD6), два других — вспомогательные (DD1, DD2 и DD3, DD4) которые запоминают состояние линии D в момент положительного перепада сигнала С и предотвращает повторное срабатывание.

Когда тактовый сигнал неактивен (С=0), оба вспомогательных триггера имеют на выходе сигнал 1 (основной триггер, таким образом, находится в режиме хранения), причем один из них находится в состоянии «включен» (на выходах логических элементов сигналы 1 и 0), а второй — в «запрещенном» состоянии 11. Какой из триггеров находится в «запрещенном» состоянии, зависит от сигнала на входе D. Так, если D=0, то триггер DD3, DD4 находится в состоянии 11, а триггер DD1, DD2 — в состоянии 10, а при D=1 наблюдается обратная картина.

Как только вход С претерпевает скачок 0→1, вспомогательные триггеры фиксируются в противофазных состояниях 10 и 01, которые не меняются ни при каких изменениях сигнала D. Соответственно, основной триггер оказывается в одном из двух состояний, в зависимости от сигнала D в момент скачка тактового сигнала.

Логические схемы троичных аналогов RS-триггера, одноступенчатого D-триггера, двухступенчатого D-триггера и счетного триггера (T-триггера) приведены на странице[26].

Логические схемы четверичных аналогов RS-триггера, одноступенчатого D-триггера, двухступенчатого D-триггера и счетного триггера (T-триггера) приведены на странице[27].

Модель пятеричного RS1S2S3S4-триггера в логическом симуляторе Atanua

Триггер с любым числом устойчивых состояний N строится из N логических элементов (N-1)ИЛИ-НЕ или (N-1)И-НЕ путем соединения выхода каждого элемента (Q0, Q1, …, Q(N-1)) с соответствующими входами всех других элементов. То есть наименьшее число логических элементов для построения N-ичного триггера равно N.

Триггеры на элементах (N-1)ИЛИ-НЕ работают в прямом одноединичном коде (на выходе Q одного из элементов — «1», на выходах Q других элементов — «0»).

Триггеры на элементах (N-1)И-НЕ работают в инверсном однонулевом коде (на выходе Q одного из элементов — «0», на выходах Q других элементов — «1»).

Эти триггеры работают как ячейки статической сверхоперативной памяти (SRAM) с управлением через N транзисторов доступа (на схеме не показаны).

При добавлении в логических элементах по одному входу и схем управления переключением эти триггеры могут работать как N-ичные аналоги двоичного RS-триггера.

В непозиционных системах счисления:

удельные затраты инверторов от числа состояний триггера не зависят: , где x1 — число инверторов, x2 — число состояний триггера.

Удельные затраты диодов в логических частях логических элементов от числа состояний триггера имеют линейную зависимость: , где x1 — число инверторов, x2

— число состояний триггера, (x2−1) — число диодов в логической части одного логического элемента. По этому параметру выгоднее двоичные триггеры.

Снимок модели пятеричного RS1S2S3S4-триггера Larry K. Baxter’а в логическом симуляторе https://intellect.icu/circus/sr-trigger

В приведенном выше подходе построения триггеров с любым числом устойчивых состояний при увеличении числа устойчивых состояний — n, увеличивается число входов в логических элементах в каждой элементарной ячейке триггера. Larry K. Baxter, Lexington, Mass. Assignee: Shintron Company, Inc., Cambridge, Mass. US Patent 3,764,919 Oct. 9, 1973 Filed: Dec. 22, 1972 Fig.3 предлагает другой подход к построению триггеров с любым числом устойчивых состояний, при котором число логических элементов и число входов в логических элементах в каждой элементарной ячейке триггера остается постоянным, но при этом увеличивается время переключения триггера пропорционально числу разрядов триггера.

Тиристор подходит для замены элемента памяти в триггерах.

Описание схемы на примере RS-триггера: К катоду тиристора подключается выход триггера Q, к управляющему электроду подключается вход S, к аноду подключается постоянное напряжение через полевой транзистор с изолированным затвором, к затвору полевого транзистора подключается вход R.

Описание работы: Начальное состояние на выходе Q ноль: тиристор находится в замкнутом состоянии, ток на выходе соответствует нулю. Переход в состояние единица: на вход S подается напряжение равно логической единице тиристор разблокируется и напряжение на выходе Q повышается соответственно логической единице, при последующем понижении напряжения на входе S тиристор сохраняет низкое сопротивление и напряжение на выходе Q остается равным логической единице. Переход от логической единицы к нулю: на вход R подается напряжение равное логической единице полевой транзистор переходит в замкнутое состояние, напряжение на аноде тиристора падает, вследствие чего сопротивление тиристора возрастает и он переходит в состояние низкого выходного напряжения соответствующего логическому нулю, это состояние сохраняется при повышении входного напряжения на аноде тиристора.

Тиристор можно заменить на два биполярных транзистора (смотря какая реализация будет удобнее).

Как итог мы получаем RS-триггер на трех транзисторах.

Несмотря на развитие электроники и особенно микроэлектроники до сих пор применяется простая логика на электромагнитных реле. Это связано с простотой реализации, высокой помехозащищенностью и хорошим уровнем электрической развязки входов и выходов таких схем по сравнению с полупроводниковой и ламповой электроникой. Но следует учитывать, что электромагнитные реле потребляют в большинстве своем значительный ток.

Таковы, например:

Рисунок 6. Классификация триггеров по типу синхронизации

Триггеры являются основными элементами цифровых систем и используются для хранения и передачи информации. Существует несколько различных типов триггеров, включая асинхронные RS-триггеры, T-триггеры, синхронные RS-триггеры, D-триггеры и JK- триггеры . Давайте рассмотрим каждый из них подробнее.

Статью про триггер я написал специально для тебя. Если ты хотел бы внести свой вклад в развитие теории и практики, ты можешь написать коммент или статью отправив на мою почту в разделе контакты. Этим ты поможешь другим читателям, ведь ты хочешь это сделать? Надеюсь, что теперь ты понял что такое триггер, асинхронный rs-триггер, t-триггеры, синхронный rs триггер, d-триггер, jk-триггер, sr-триггер, flip-flop и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Электроника, Микроэлектроника , Элементная база

Комментарии

Оставить комментарий

Электроника, Микроэлектроника , Элементная база

Термины: Электроника, Микроэлектроника , Элементная база