Лекция

Сразу хочу сказать, что здесь никакой воды про цифровые запоминающие устройства, и только нужная информация. Для того чтобы лучше понимать что такое цифровые запоминающие устройства, параллельный регистр, регистры памяти на триггерах, характеристики зу, классификация зу, запоминающие устройства, озу , настоятельно рекомендую прочитать все из категории Электроника, Микроэлектроника , Элементная база.

Запоминающее устройство (ЗУ) — устройство, предназначенное для записи и хранения данных. В основе работы запоминающего устройства может лежать любой физический эффект, обеспечивающий приведение системы к двум или более устойчивым состояниям. Устройство, реализующее компьютерную память.

Цифровые запоминающие устройства — устройства, предназначенные для записи, хранения и считывания информации, представленной в цифровом коде.

К основным параметрам цифровых ЗУ относятся информационная емкость (битов, тритов и т. д.), потребляемая мощность, время хранения информации, быстродействие.

Самое большое распространение цифровые запоминающие устройства приобрели в компьютерах (компьютерная память). Кроме того, они применяются в устройствах автоматики и телемеханики, в приборах для проведения экспериментов, в бытовых устройствах (телефонах, фотоаппаратах, холодильниках, стиральных машинах и т. д.), в пластиковых карточках, замках.

Ёмкость двоичных цифровых запоминающих устройств измеряется в битах.

Ёмкость троичных цифровых запоминающих устройств измеряется в тритах.

Устройства, предназначенные для записи, Хранения и считывания информации, представленной в цифровом коде. Подразделяются на оперативные ( озу ) и постоянные (ПЗУ).

ОЗУ обеспечивает режим записи, хранения и считывания информации в процессе ее обработки.

ПЗУ в рабочем режиме допускает только считывание информации.

К основным параметрам ЗУ относятся информационная емкость(бит), потребляемая мощность (Вт), время хранения информации (час), быстродействие и т,д.

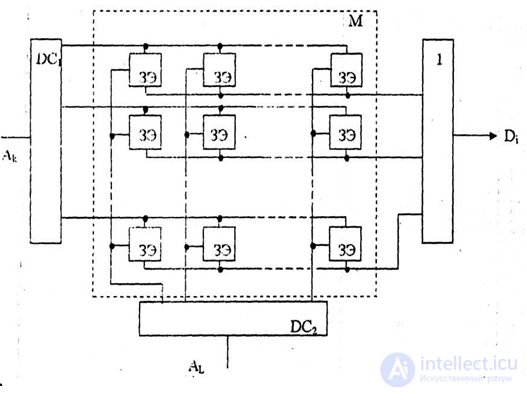

Основой ЗУ является матрица памяти (накопитель), состоящая из запоминающих элементов (ЗЭ), а гак же устройства, позволяющие записывать и считывать информацию с каждого ЗЭ матрицы. В качестве примера рассмотрим ЗУ с двумерной адресацией для записи одноразрядных чисел (слов). Увеличение разрядности достигается параллельном подключением нескольких подобных ЗУ.

Матрица ЗУ содержит «п» столбцов и «m» строк, выбор которых осуществляется дешифраторами DC1 и DC2 в соответствии с адресным кодом, подаваемым на входы дешифраторов. Таким образом вбирается запоминающий элемент, находящийся на пересечении акпишых выходов обоих дешифраторов. В зависимости от подключения ЗЭ к шинам столбцов и арок, при этом может осуществляться запись или считывание информации с каждой ячейки памяти. Например, ЗЭ может представлять собой D триггер, информационный вход которого подключен к шине строк, а вход синхронизации к шине столбцов. Тогда состояние триггера соответствует «1» (запись) только при наличии сигналов «1» на обоих входах. Считывание информации с. ЗЭ может осуществляться с помощью «т» входового (по числу строк) элемента ИЛИ, притом дешифраторы подают сигналы на входы ЗЭ, разрешающие считывание информации. Запоминающее устройство (ЗУ) может иметь и другую структуру, например структура ЗУ с Одномерной адресацией представляет собой матрицу, число строк которой соответствует числу хранимых чисел (слои), а число столбцов - их разрядности. В этом случае требуется один дешифратор, однако он должен иметь большое количество выводов, что усложняет аппаратную реализацию.

регистры памяти на триггерах

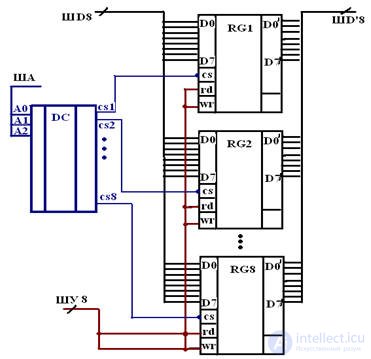

CS - всегда активный инверсный вход выбора схемы.

RG регистр запоминает 8 бит информации.

Если поставить 8 регистров, то получим память на 8 байт

На ШУ: «0» - чтение RD, «1» - запись WR

параллельный регистр

Если поставить много регистровRG1-RG8, то необходим позиционный дешифратор DC для выбора регистра на чтение или запись информации.

Например: хотим прочитать данные с RG1 для этого на вход RDRG1 подаем «1», на ША идет код адреса выбора RG1, т.е. Об этом говорит сайт https://intellect.icu . «0» на выходеcs1 дешифратора на всех остальных «1».

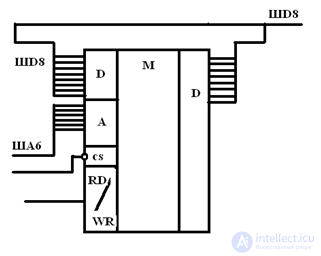

Объединяя в одной МС дешифратор и регистры, получают микросхему постоянной памяти.

Такие МС имеют одну ШD, которая разделена сигналами RD/WR, т.е. ШD двунаправленная.

В процессорах всегда ШD на 8 проводов, в ЭВМ на 16, 32, 64, современные сопроцессоры 96

В МСП адресов 4096, с конфигурацией 4096×8 ШУ имеет обычно 10-50 проводов

Пример1: ША на 64 регистра, конфигурация 64×8

Пример 2

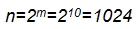

Определить информационную емкость n МСП, если число адресных входов m=10

Оперативная память ( англ. Random Access Memory , дословно — память с произвольным доступом , ПДД , первичная память) — память компьютера , предназначенная для хранения кода и данных программ при их выполнении . В современных компьютерах оперативная память преимущественно представлена динамической памятью с произвольным доступом DRAM .

Противоположностью памяти с произвольным доступом является память с последовательным доступом . При произвольном доступе память организована таким образом, что в любой момент можно получить значение, записанное в любой ячейке памяти, не просматривая другие ячейки. При памяти с последовательным доступом, реализуемой, например, на магнитной ленте , для доступа к определенному элементу памяти нужно прокрутить ленту, считывая другие элементы.

Виды памяти произвольным доступом:

Однако к 2003 году появилась магниторезистивная оперативная память (MRAM) в интегральном исполнении. Сочетая скорость SRAM и возможность хранения информации при отключенном питании, MRAM является перспективной заменой типам ROM и RAM. Однако она примерно вдвое дороже микросхем SRAM (при той же емкости и габаритах).

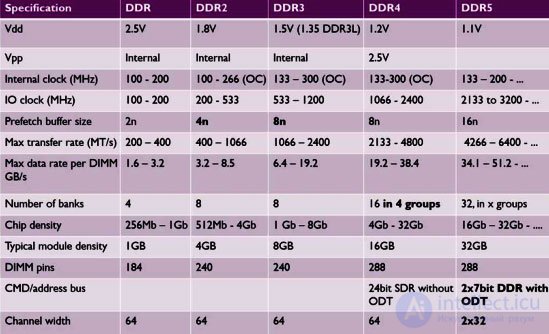

DDR5 SDRAM — пятое поколение оперативной памяти , являющееся эволюционным развитием предыдущих поколений DDR SDRAM . Планируется, что DDR5 уменьшит энергопотребление, а также будет иметь удвоенную пропускную способность и объем по сравнению с DDR4 SDRAM .

Корпорация Intel в выступлении 2016 года предполагала, что JEDEC может выпустить спецификацию DDR5 SDRAM в 2016 году, с коммерческой доступностью памяти до 2020 года .

В марте 2017 года JEDEC сообщила о планах выпустить спецификацию DDR5 в 2018 году. ] На форуме JEDEC Server 2017 сообщалось о дате предварительного доступа к описанию DDR5 SDRAM с 19 июня 2017 года, а 31 октября начался двухдневный «DDR5 SDRAM Workshop». Компания Rambus анонсировала прототип памяти DDR5 RAM в сентябре 2017 года, с доступностью не ранее 3 квартала 2018 года. Micron изготовила первые прототипы памяти в 2017 году, они были проверены с помощью контроллера Cadence ( TSMC , 7 нм) .

В продажу первые коммерческие модули DDR5 (DDR5-4800) объемом 16 Гб от Team Group поступили 28 июня 2021 г. по цене $310,99. Они требовали всего 1,1 вольта для работы и не имели радиатора

Оперативные запоминающие устройства (ОЗУ, RAM).

Предназначены для записи, хранения и считывания информации в процессе ее обработки.

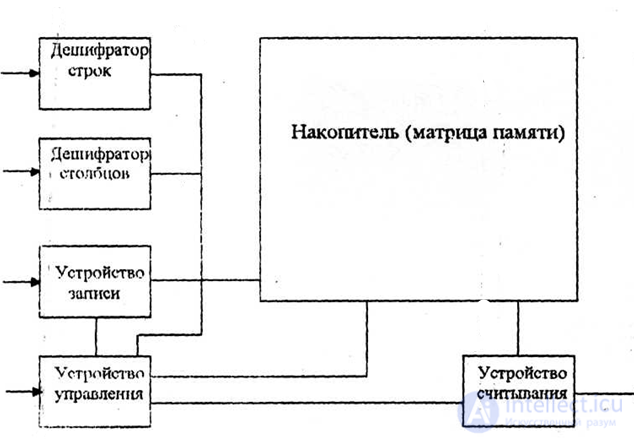

Подразделяются па статические и динамические. В статических ОЗУ запоминающий элемент представляет собой триггер, изготовленные по той или иной технологии (ТТЛ, КМОП и др.), что позволяет считывание информации без ее разрушения (потери).В динамических ОЗУ элементом памяти является емкость (например, входная емкость полевого транзистора),что требует восстановления (регенерации) записанной информации в процессе ее хранения и использования. Это усложняет применение ОЗУ динамического типа, но позволяет реализовать больший объем памяти. В современных динамических ОЗУ имеются встроенные системы синхронизации и регенерации, поэтому по внешним сигналам управления они не отличаются от статических. Блок схему ОЗУ можно представить в следующем виде:

Здесь дешифраторы строк и столбцов подключаются к матрице памяти устройством управления через устройство записи или устройство считывания, чем и определяется режим работы ОЗУ

Статические параметры ЗУ

Динамические параметры ЗУ:

Классификации ЗУ:

по функциональному назначению

по способу хранения информации

по технологии изготовления

по способу обращения к массиву элементов памяти

Статью про цифровые запоминающие устройства я написал специально для тебя. Если ты хотел бы внести свой вклад в развитие теории и практики, ты можешь написать коммент или статью отправив на мою почту в разделе контакты. Этим ты поможешь другим читателям, ведь ты хочешь это сделать? Надеюсь, что теперь ты понял что такое цифровые запоминающие устройства, параллельный регистр, регистры памяти на триггерах, характеристики зу, классификация зу, запоминающие устройства, озу и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Электроника, Микроэлектроника , Элементная база

Комментарии

Оставить комментарий

Электроника, Микроэлектроника , Элементная база

Термины: Электроника, Микроэлектроника , Элементная база