Лекция

Привет, Вы узнаете о том , что такое цифровые схемы, Разберем основные их виды и особенности использования. Еще будет много подробных примеров и описаний. Для того чтобы лучше понимать что такое цифровые схемы , настоятельно рекомендую прочитать все из категории Электроника, Микроэлектроника , Элементная база.

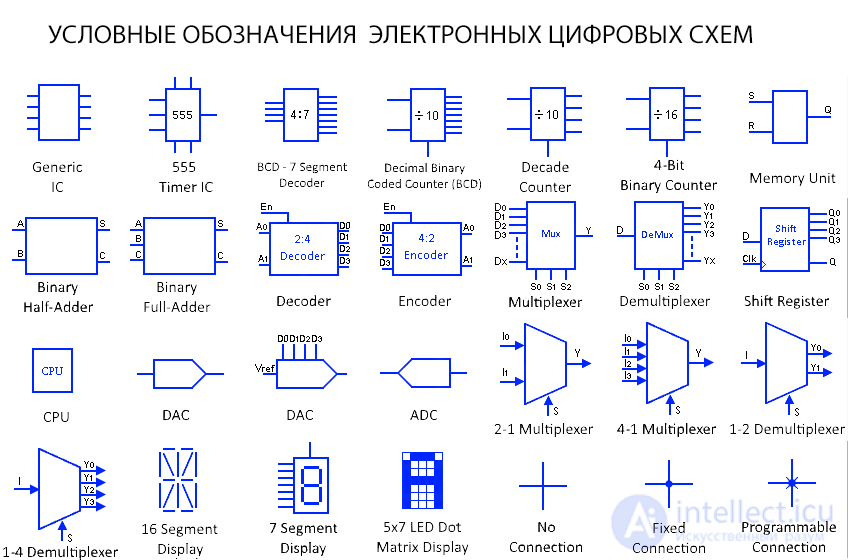

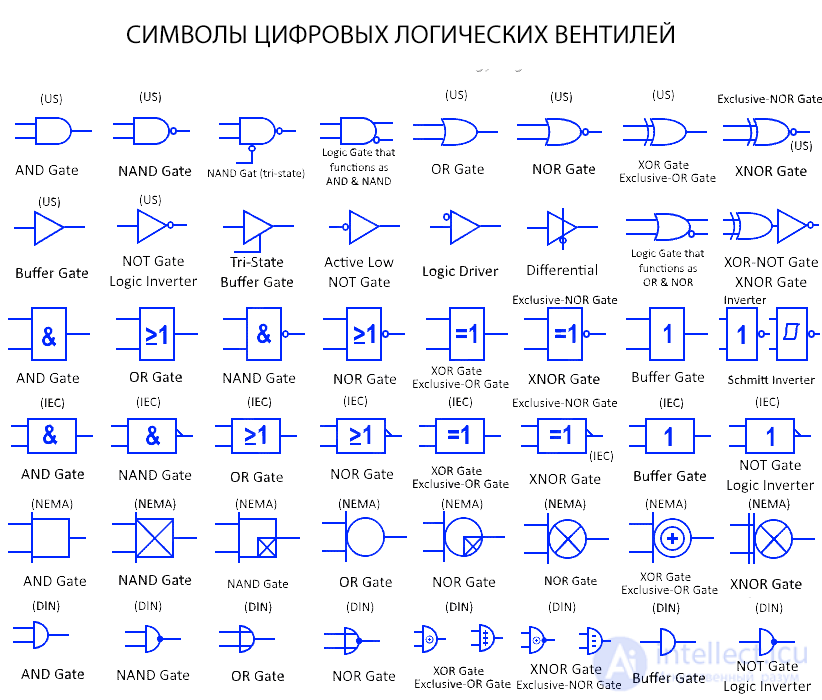

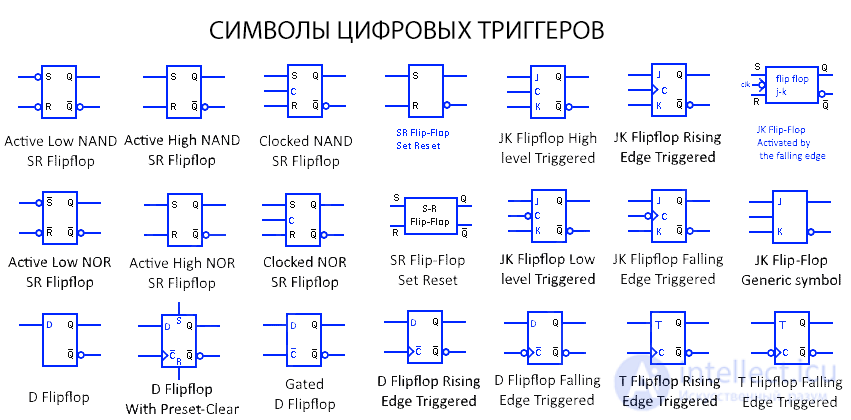

Для обозначения элементов в электронных цифровых схемах используют стандартные условные графические символы. Они помогают инженерам и разработчикам точно идентифицировать компоненты и их функции. Вот несколько ключевых условных обозначений:

Логические элементы:

Триггеры:

Цифровые шины и соединения:

Тактовые сигналы:

Если вы разрабатываете или симулируете цифровую схему, эти условные обозначения помогут вам организовать проект и облегчат работу с онлайн симуляторами.

Общий символ IC

Это символ общей ИС (интегральной схемы) . Это небольшой чип, изготовленный из полупроводникового материала, на котором изготовлено несколько микроэлектрических компонентов для выполнения определенной задачи и уменьшения размера.

555 Таймер ИС

Это символ для 555 Timer IC . Он имеет три режима работы, а именно: астабильный (генератор), моностабильный (таймер) и бистабильный (триггер). Это наиболее используемая ИС во всем мире, и ее применение безгранично в зависимости от режимов, в которых они используются.

Декодер BCD в 7 сегментов

Это символ для декодера BCD в 7-сегментный дисплей . Он преобразует двоично-десятичный код, который представляет собой 4-битный двоичный сигнал, в 7 выходных линий, каждая из которых управляет отдельным сегментом 7-сегментного дисплея.

4-битный двоичный счетчик

Это простой 4-битный двоичный счетчик , который считает от 0 до 15, а затем сбрасывается до 0. Он работает от тактового сигнала и на каждом тактовом цикле он увеличивается на одну цифру. Число 16 представляет собой число MOD, т.е. максимальное число состояний, которые он имеет. Он делит частоту тактового сигнала на это число.

Счетчик декад

Это символ для цифрового Десятичного счетчика, также известного как делитель частоты. Он считает от 0 до 9, а затем сбрасывается вместо подсчета в двоичных цифрах. Каждый тактовый цикл на входе увеличивает выход на 1. Этот Десятичный счетчик делит входную частоту (входной тактовый сигнал) на 10.

Базовый блок памяти

Это базовый блок памяти, строительный блок блока памяти в любом устройстве. Это защелка SR, которая хранит один бит данных. SR означает функцию установки и сброса защелки.

Двоичный полусумматор

Схема полусумматора складывает два однобитовых двоичных входа A и B и выдает их сумму S и бит переноса C. Причина, по которой она называется полусумматором, заключается в том, что она не может учитывать перенос из предыдущих сложений.

Двоичный полный сумматор

Это символ для цифрового двоичного полного сумматора. Он складывает два однобитовых двоичных числа A и B и обеспечивает их сумму S переносом C. Полный сумматор также добавляет перенос из предыдущего сложения, поэтому он называется полным сумматором. Несколько полных сумматоров сложены вместе для выполнения сложения многобитовых чисел.

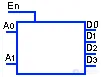

2-4 цифровой декодер

Декодер преобразует n-битный двоичный вход в соответствующие 2 n десятичных выходных линий. Выходные линии декодера всегда имеют низкий уровень, за исключением одной линии. Этот декодер преобразует двоичный вход двух бит A 0 и A 1 в 4 десятичных кодированных выхода D 0 , D 1 , D 2 , D 3 . Комбинация входной логики A 0 и A 1 решает, какая из выходных линий станет логической высокой. Вход Enable включает и выключает схему.

Цифровой кодер 4 в 2

Цифровой кодер преобразует 2 n десятичных входных линий в n двоичных выходных линий. На входных линиях данных D должен быть только один высокий вход. В соответствии с десятичными входными линиями генерируется выход в двоичном коде.

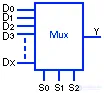

Мультиплексор или Mux

Цифровой мультиплексор или Mux — это многовходовое одновыходное устройство. Это цифровой селекторный переключатель, который выбирает один выход из нескольких входных линий данных. Двоичные комбинации селекторных битов S 0 …S 2 выбирают определенную линию данных D 0 …D x в качестве выхода Y. Например, для S = 010, Y = D 2 и для S = 110, Y = D 6 .

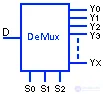

Демультиплексор или DeMux

Демультиплексор или ДеМультиплексор — это устройство с одним входом и несколькими выходами. Он также является селекторным переключателем и работает противоположно мультиплексору. Он имеет одну линию ввода данных D и передает ее на одну из нескольких линий вывода Y 0 …Y x , которая выбирается с помощью битов селектора S 0 …S 2 .

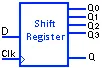

Сдвиговый регистр

Это блок памяти, состоящий из триггера, который используется для хранения временных данных в цифровых устройствах. Входные данные последовательно подаются в сдвиговый регистр через входную линию D, которая хранится в триггере. Доступ к данным, хранящимся в сдвиговом регистре, может осуществляться как последовательно, так и параллельно с использованием Q и Q 0 … Q 3 соответственно.

Процессор

ЦП означает Центральный процессор, также известный как процессор, это чип внутри компьютера. Это мозг компьютера, который выполняет задачи, выполняя инструкции, выполняемые программой.

ЦАП

Это общий символ ЦАП, показывающий только его вход и выход. ЦАП, также известный как цифро-аналоговый преобразователь, представляет собой электронную ИС, которая преобразует любой цифровой сигнал в аналоговый сигнал. Они используются в таких системах, где устройство не может работать с цифровыми данными, поэтому ЦАП преобразует сигнал в аналоговый.

ЦАП с цифровым входом

Это подробный символ ЦАП, показывающий входные порты для цифрового сигнала в двоичной форме и Vref, который является опорным напряжением для генерируемого выходного аналогового сигнала.

АЦП

Это общий символ АЦП. АЦП означает аналого-цифровой преобразователь . Он работает в точности наоборот ЦАП. Он преобразует любой аналоговый сигнал в цифровой сигнал в двоичном формате. Он используется почти во всех цифровых устройствах, которые в какой-то степени зависят от аналоговых данных.

Мультиплексор 2 в 1

Это символ мультиплексора 2 в 1 или Mux, который является цифровым устройством, имеющим несколько входов и один выход. Вход селектора S выбирает вход I 0 или I 1 в качестве выхода Y.

Мультиплексор 4 в 1

Это символ мультиплексора 4 в 1. Он выбирает одну из 4 входных линий, которая проходит через выход Y. Вход селектора S используется для выбора входной линии.

1 к 2 Демультиплексор

Это символ демультиплексора 1 в 2, используемого для передачи одной входной линии на две отдельные выходные линии. Селекторный переключатель S выбирает одну из двух выходных линий.

1-4 Демультиплексор

Этот символ используется для демультиплексора 1–4. Он показывает одну входную линию I, переданную на одну из 4 выходных линий Y, которая выбирается селекторным входом S.

Шестнадцатисегментный дисплей

Это символ шестнадцатисегментного дисплея, также известного как SISD. Он имеет шестнадцать светодиодов, сконфигурированных в такой геометрии для отображения символов, таких как арабские цифры, тайские цифры и латинские буквы и т. д.

Семисегментный дисплей

Это семисегментный дисплейный символ. Он используется для отображения десятичных цифр и английских букв. Однако он может быть разработан для отображения многочисленных символов.

Светодиодный матричный дисплей 5×7

Это символ 5×7 матричного дисплея. Он имеет 5 столбцов и 7 рядов светодиодов в форме точек, расположенных рядом друг с другом. Он используется для отображения символов и фигур в цифровых устройствах.

Нет связи

Это символическое изображение двух проводов или дорожек в цифровой цепи или схеме, которые не связаны друг с другом.

Фиксированное соединение

Это визуальное представление, показывающее соединение между двумя проводами или дорожками на схеме.

Программируемое подключение предохранителя

Это символ программируемого соединения. Это соединение предназначено для закрытия или открытия путем перегорания предохранителя посредством программирования.

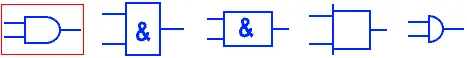

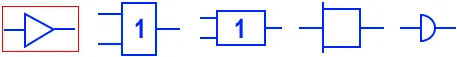

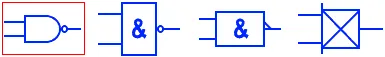

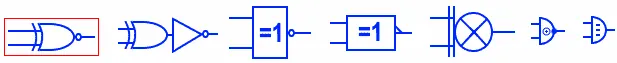

В цифровых логических схемах используются стандартные символы для обозначения различных логических вентилей. Вот основные из них:

AND (И):

OR (ИЛИ):

NOT (НЕ):

NAND (И-НЕ):

NOR (ИЛИ-НЕ):

XOR (ИСКЛЮЧАЮЩЕЕ ИЛИ):

XNOR (ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ):

Цифровой логический вентиль «И»

И -вентиль выполняет логическую (включающую) конъюнкцию (выход True только если все входы True). Он обеспечивает выходную логику «HIGH» только тогда, когда все его входы имеют логику «HIGH». И он обеспечивает логику «LOW», когда один или все входы имеют логику «LOW».

Цифровой логический вентиль ИЛИ

Вентиль ИЛИ выполняет логическую (включающую) дизъюнкцию (истинный выход для любого истинного входа). Выход вентиля ИЛИ имеет логический «ВЫСОКИЙ», когда один или более чем один из его входов имеет логический «ВЫСОКИЙ». Выход остается логическим «НИЗКИМ» только тогда, когда все его входы имеют логический «НИЗКИЙ».

Цифровой логический вентиль НЕ

НЕ-вентиль, также известный как логический инвертор, представляет собой логический вентиль с одним входом и одним выходом. Он инвертирует входную логику. Выходной сигнал имеет логический уровень «НИЗКИЙ», когда входной сигнал имеет логический уровень «ВЫСОКИЙ», а выходной сигнал имеет логический уровень «ВЫСОКИЙ», когда входной сигнал имеет логический уровень «НИЗКИЙ».

Активный низкий уровень НЕ-ворот

Пузырь перед вентилем показывает, что это активный низкий логический вентиль. Он имеет ту же функцию, что и обычный вентиль НЕ .

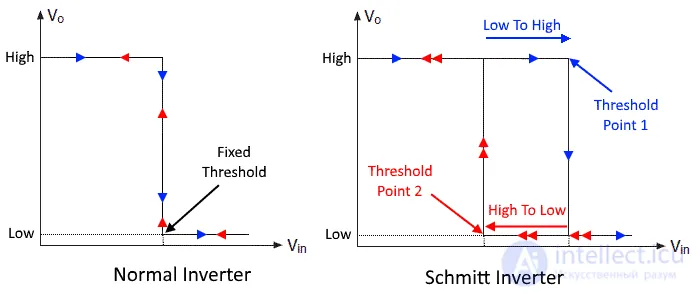

Инвертор Шмитта:

Инвертор Шмитта — это логический вентиль, разработанный с использованием явления гистерезиса, возникающего из-за положительной обратной связи внутри вентиля. Основное различие между обычным инвертором и инвертором Шмитта заключается в его пороговом уровне. Первый имеет фиксированный порог, который определяет НИЗКУЮ и ВЫСОКУЮ логику, последний имеет пороговый уровень, который напоминает кривую гистерезиса BH, т. е. порог от низкого до высокого и от высокого до низкого отличается.

Цифровой буферный шлюз

Буферный вентиль имеет один вход и один выход. Он не изменяет входную логику. Он в основном используется для увеличения задержки распространения сигнала.

Цифровой буферный затвор с тремя состояниями

Такой тип буферного затвора имеет дополнительный контрольный вывод (также известный как разрешающий вывод). Он используется для управления потоком логики. Если контрольный вывод ВЫСОКИЙ, входная логика вытекает, в противном случае выход — «Состояние высокого импеданса Z».

Цифровой логический элемент NAND

Элемент NAND является обратным элементу AND или элементом «НЕ AND». Его выход имеет логический уровень «High», когда любой из входов имеет логический уровень «LOW», а его выход имеет логический уровень «LOW», когда все его входы имеют логический уровень «HIGH».

Цифровой логический элемент ИЛИ-НЕ

NOR-вентиль является отрицательным или обратным OR-вентилю или «НЕ ИЛИ-вентилю». Об этом говорит сайт https://intellect.icu . Он выдает логику «ВЫСОКИЙ», когда все его входы имеют логику «НИЗКИЙ» и выдает логику «НИЗКИЙ», когда любой из входов имеет логику «Высокий».

Цифровой логический элемент XOR

XOR Gate, также известный как Exclusive OR Gate, реализует исключающую дизъюнкцию (выход true, когда только один вход true). Выход XOR-вентиля имеет ВЫСОКИЙ уровень, когда только один вход имеет ВЫСОКИЙ уровень, в противном случае выход LOW.

Цифровой логический элемент XNOR

XNOR Gate , также известный как Exclusive NOR Gate, является инвертированием XOR gate. Он реализует функцию равенства. Выходной сигнал True только в том случае, если логика входов одинакова, т.е. выходной сигнал HIGH только тогда, когда все входы имеют уровень «HIGH» или «LOW».

Подразумеваемый Гейт

Логический вентиль IMPLY реализует « логическое условие ». Он формирует утверждение «Если A, то B».

Выход этого вентиля: «если вход A истинен, то вход B также истинен». Так что, когда A истинен «HIGH» и B истинен «HIGH», выход истинен «HIGH». Когда A истинен, но B ложен, то выход ложен. Теперь, если вход A ложен, то выход автоматически становится истинным независимо от входа B, т.е. выход истинен в обоих случаях.

| А | Б | Выход |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

NIMPLY ворота

Логический вентиль NIMPLY имеет инвертированный выход логического вентиля IMPLY. Он реализует утверждение «Если A, но не B». Это означает, что выход истинен тогда и только тогда, когда вход A истинен, но B ложен.

| А | Б | Выход |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

В цифровых схемах триггеры используются для хранения и управления состоянием битов. Вот основные символы для различных типов триггеров:

D-триггер (Data или Delay Flip-Flop):

JK-триггер:

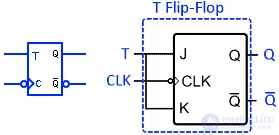

T-триггер (Toggle Flip-Flop):

SR-триггер (Set-Reset Flip-Flop):

D-триггер с асинхронным сбросом и установкой:

Триггеры и защелки — это последовательные схемы, и они являются строительным блоком для блоков памяти. Они хранят один бит данных. Выход последовательной схемы зависит не только от ее текущего (текущего) входа, но и от ее предыдущего выхода.

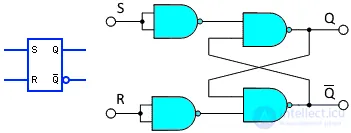

Асинхронный триггер NAND с активным низким SR

Этот SR-триггер, также известный как SR-защелка, представляет собой асинхронную (независимую от тактового сигнала) последовательную схему, состоящую только из вентилей NAND. SR представляет функцию «установки и сброса» триггера. Пузырьки на входе показывают, что он активен на низком уровне .

Когда оба 'S' и 'R' имеют НИЗКИЙ уровень, состояние считается недействительным, т.е. выход не определен. Это недействительное состояние и его избегают.

| С | Р | Состояние | Вопрос следующий | Вопрос ' |

| 1 | 1 | Состояние удержания (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 0 | 1 | Набор | 1 | 0 |

| 1 | 0 | Перезагрузить | 0 | 1 |

| 0 | 0 | Неверный | Х | Х |

Активный триггер NAND с высоким SR

Этот триггер SR работает так же, как активный низкий триггер SR, за исключением того, что его входы инвертируются с помощью вентилей NAND и инверторов. Это позволяет триггеру работать при активных высоких входах.

| С | Р | Состояние | Вопрос следующий | Вопрос ' |

| 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 0 | Набор | 1 | 0 |

| 0 | 1 | Перезагрузить | 0 | 1 |

| 1 | 1 | Неверный | Х | Х |

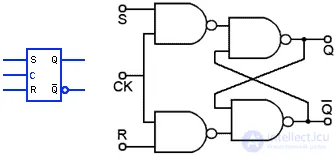

Тактовый SR NAND ٖFlip-ٖٖٖٖFlop

| КЛК | С | Р | Состояние | Вопрос следующий | Вопрос ' |

| 0 | Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 1 | 0 | Набор | 1 | 0 |

| 1 | 0 | 1 | Перезагрузить | 0 | 1 |

| 1 | 1 | 1 | Неверный | Х | Х |

Синхронизированный SR-триггер или также известный как стробируемый SR-триггер — это модифицированный SR-триггер с управляющим входом. Тактовый вход управляет состоянием триггера. Когда C = 0, SR-триггер сохраняет свое предыдущее состояние, т.е. остается в состоянии удержания. Когда C = 1, SR-триггер работает как обычный активный высокий триггер.

Они используются для синхронизации с другими цепями, использующими общий тактовый сигнал.

SR NOR Триггер Активный Низкий

Этот триггер SR сделан из четырех вентилей NOR. Два вентиля NOR в начале действуют как инвертор, который преобразует этот триггер в активный низкий триггер. Полоска на входных сигналах показывает, что вход инвертирован (активный низкий).

| С | Р | Состояние | Вопрос следующий | Вопрос ' |

| 1 | 1 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 0 | 1 | Набор | 1 | 0 |

| 1 | 0 | Перезагрузить | 0 | 1 |

| 0 | 0 | Неверный | Х | Х |

SR NOR триггер активный высокий

Этот SR-триггер сделан всего из двух вентилей NOR. Он работает так же, как SR-триггер сделанный из вентилей NAND, но он активен на высоком уровне.

| С | Р | Состояние | Вопрос следующий | Вопрос ' |

| 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 0 | Набор | 1 | 0 |

| 0 | 1 | Перезагрузить | 0 | 1 |

| 1 | 1 | Неверный | Х | Х |

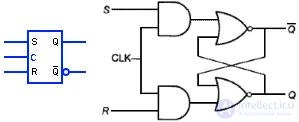

Синхронизированный SR NOR ٖтриггер

Это тактируемый SR-триггер, использующий вентили NOR. Вентили AND используются для управления входным сигналом. Когда сигнал CLK ВЫСОКИЙ, входной сигнал поступает и триггер работает нормально. Когда сигнал CLK НИЗКИЙ, триггер остается в состоянии удержания относительно сигналов S и R.

| КЛК | С | Р | Состояние | Вопрос следующий | Вопрос ' |

| 0 | Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 1 | 0 | Набор | 1 | 0 |

| 1 | 0 | 1 | Перезагрузить | 0 | 1 |

| 1 | 1 | 1 | Неверный | Х | Х |

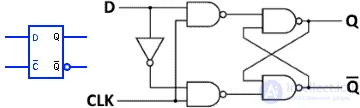

D-шлепанцы

D-триггер также известен как триггер «DATA» или «DELAY». Это модифицированная версия SR-триггера с одним общим входом D. Он хранит один бит данных из входной линии D.

Когда D = 0, триггер сбрасывается и выход Q становится 0. Когда D = 1, выход устанавливается и Q становится 1.

| Д | Состояние | Вопрос следующий | Вопрос ' |

| 0 | Перезагрузить | 0 | 1 |

| 1 | Набор | 1 | 0 |

Закрытый D-триггер (срабатывает по уровню)

Управляемый D-триггер или также известный как D-триггер срабатывающий по уровню имеет дополнительный управляющий вход, известный как вход «Enable» или «clock». Когда CLK = 0, D-триггер сохраняет предыдущее состояние. Когда CLK = 1, он работает как обычный D-триггер.

| КЛК | Д | Состояние | Вопрос следующий | Вопрос ' |

| 0 | Х | Держать | Предыдущее состояние | Предыдущее состояние |

| 1 | 0 | Перезагрузить | 0 | 1 |

| 1 | 1 | Набор | 1 | 0 |

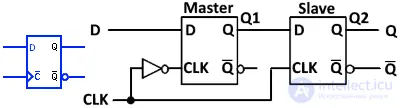

D-триггер срабатывает по восходящему фронту

D-триггер с фронтом также известен как ведущий-ведомый D-триггер. Он чувствителен к фронту тактового сигнала и обновляет свое значение только при обнаружении фронта тактового сигнала.

Он может быть разработан для нарастающего или падающего фронта. Это D-триггер, запускаемый нарастающим фронтом. При нарастающем фронте CLK применяется к ведомому триггеру Q2, а CLK' применяется к ведущему триггеру.

Этот триггер, запускаемый по переднему фронту, обновляет свое состояние только по переднему фронту тактового сигнала. До тех пор он будет сохранять свое состояние.

| КЛК | Д | Состояние | Вопрос следующий | Вопрос ' |

| Х | Х | Держать | Предыдущее состояние | Предыдущее состояние |

| Восходящий фронт | 0 | Перезагрузить | 0 | 1 |

| Восходящий фронт | 1 | Набор | 1 | 0 |

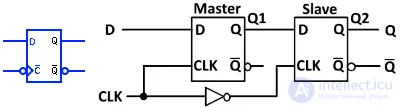

D-триггер срабатывает по заднему фронту

D-триггер, запускаемый по заднему фронту, обновляет свое состояние только при заднем фронте тактового сигнала. Триггер сохраняет свое предыдущее состояние до заднего фронта тактового сигнала.

В триггере, запускаемом по заднему фронту, CLK подается на главный триггер, а CLK' подается на подчиненный триггер.

| КЛК | Д | Состояние | Вопрос следующий | Вопрос ' |

| Х | Х | Держать | Предыдущее состояние | Предыдущее состояние |

| Падающий фронт | 0 | Перезагрузить | 0 | 1 |

| Падающий фронт | 1 | Набор | 1 | 0 |

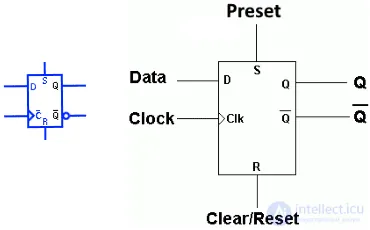

D-Flip Flop с предустановками и сбросом настроек

Это D-триггер с фронтом с функцией Preset (SET) и Clear (Reset). Он работает так же, как любой D-триггер с фронтом. Входы Preset и Clear устанавливают и сбрасывают триггер соответственно (как и SR-триггер) независимо от фронта тактового сигнала. Установка и предустановка могут быть разработаны для входов Active Low и Active High.

| КЛК | Д | Предустановленный | Прозрачный | Состояние | Вопрос следующий | Вопрос ' |

| Х | Х | 1 | 0 | Предустановленный | 1 | 0 |

| Х | Х | 0 | 1 | Прозрачный | 0 | 1 |

| Х | Х | 0 | 0 | Держать | Предыдущее состояние | Предыдущее состояние |

| Восходящий фронт | 0 | 0 | 0 | Перезагрузить | 0 | 1 |

| Восходящий фронт | 1 | 0 | 0 | Набор | 1 | 0 |

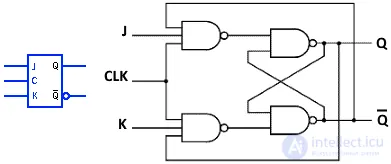

JK Flip Flop Высокий уровень срабатывания

Триггер JK является модифицированной версией триггера SR. Запрещенный (недопустимый) вход в триггере SR используется в триггере JK для функции переключения. За исключением функции переключения триггер JK работает так же, как триггер SR.

Поскольку это триггер высокого уровня, сигнал CLK активирует триггер, когда CLK = 1. Триггер сохраняет свое состояние, когда CLK = 0.

Вот таблица истинности для триггера JK с высоким уровнем срабатывания

| КЛК | Дж. | К | Состояние | Вопрос следующий | Вопрос ' |

| 0 | Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 1 | 1 | 0 | Набор | 1 | 0 |

| 1 | 0 | 1 | Перезагрузить | 0 | 1 |

| 1 | 1 | 1 | Переключить состояния | Вопрос ' | В |

Триггер JK Flip Flop сработал на низком уровне

Триггер JK низкого уровня активируется низким уровнем импульса CLK. Когда CLK = 0, триггер активируется, и состояние триггера обновляется в соответствии с входом J и K. Когда CLK = 1, триггер сохраняет свое предыдущее состояние независимо от входа J и K.

| КЛК | Дж. | К | Состояние | Вопрос следующий | Вопрос ' |

| 1 | Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 0 | 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| 0 | 1 | 0 | Набор | 1 | 0 |

| 0 | 0 | 1 | Перезагрузить | 0 | 1 |

| 0 | 1 | 1 | Переключить состояния | Вопрос ' | В |

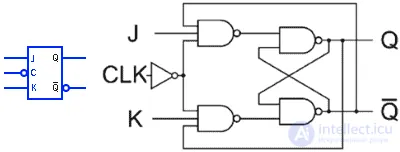

JK Flip Flop срабатывает по восходящему фронту

Триггер JK с запуском по фронту разработан путем работы двух триггеров JK с запуском по уровню в комбинации Master-Slave. Они имеют ту же функцию, что и триггер с запуском по уровню, за исключением того, что они активируются только при наличии фронта тактового сигнала.

Триггер, запускаемый по восходящему или положительному фронту, активируется по восходящему фронту тактового сигнала (от низкого 0 до высокого 1). Он разработан путем соединения CLK с ведущим триггером и CLK' с ведомым триггером.

| КЛК | Дж. | К | Состояние | Вопрос следующий | Вопрос ' |

| Х | Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Восходящий Край | 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Восходящий Край | 1 | 0 | Набор | 1 | 0 |

| Восходящий Край | 0 | 1 | Перезагрузить | 0 | 1 |

| Восходящий Край | 1 | 1 | Переключить состояния | Вопрос ' | В |

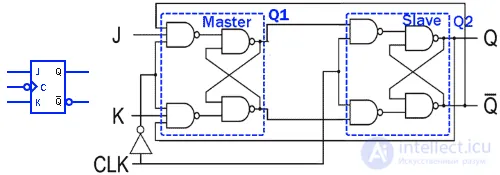

JK Flip Flop Срабатывание по падающему фронту

Триггер JK, запускаемый по заднему фронту, активируется задним фронтом тактового сигнала.

В триггере JK, запускаемом по заднему фронту, CLK подключен к подчиненному триггеру Q2, а CLK' подается на главный триггер Q1. Всякий раз, когда обнаруживается задний фронт, т. е. от высокого 1 до низкого 0, триггер обновляет свое состояние в соответствии с входами J и K. В противном случае триггер сохраняет свое состояние, несмотря ни на что.

| КЛК | Дж. | К | Состояние | Вопрос следующий | Вопрос ' |

| Х | Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Падающий край | 0 | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Падающий край | 1 | 0 | Набор | 1 | 0 |

| Падающий край | 0 | 1 | Перезагрузить | 0 | 1 |

| Падающий край | 1 | 1 | Переключить состояния | Вопрос ' | В |

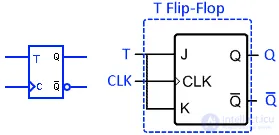

T-триггер срабатывает по восходящему фронту

T-триггер представляет собой триггер «Toggle» и является модифицированной версией JK-триггера. Входы J и K JK-триггера объединены вместе, образуя один вход «T».

T-триггер меняет свое состояние, когда T = 1, т.е. Q = Q'. Когда T = 0, триггер сохраняет свое предыдущее состояние.

Так как это T-триггер с нарастающим фронтом, триггер будет переключаться только при наличии положительного фронта тактового сигнала, т.е. тактовый сигнал изменится с 0 на 1. В противном случае триггер останется в состоянии удержания.

| КЛК | Т | Состояние | Вопрос следующий | Вопрос ' |

| Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Восходящий Край | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Восходящий Край | 1 | Переключить состояния | Вопрос ' | В |

T-триггер Flip Flop, срабатывающий по заднему фронту

Триггер T, запускаемый по заднему фронту, создан путем соединения входов (J и K) триггера JK, запускаемого по заднему фронту. Он активируется при обнаружении заднего фронта в тактовом сигнале, в противном случае триггер сохранит свое предыдущее состояние независимо от входной логики.

| КЛК | Т | Состояние | Вопрос следующий | Вопрос ' |

| Х | Х | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Падающий край | 0 | Удержание (без изменений) | Предыдущее состояние | Предыдущее состояние |

| Падающий край | 1 | Переключить состояния | Вопрос ' | В |

Исследование, описанное в статье про цифровые схемы, подчеркивает ее значимость в современном мире. Надеюсь, что теперь ты понял что такое цифровые схемы и для чего все это нужно, а если не понял, или есть замечания, то не стесняйся, пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Электроника, Микроэлектроника , Элементная база

Комментарии

Оставить комментарий

Электроника, Микроэлектроника , Элементная база

Термины: Электроника, Микроэлектроника , Элементная база